# 전자회로

< 강의노트 >

2019. 3.

안 상 호

인제대학교

전자IT기계자동차공학부 전자공학과

# Chap. 2 The pn junction

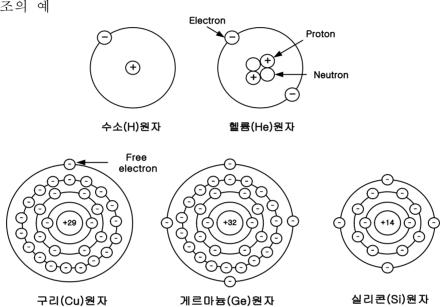

### ■ 원자구조

- 원자(atom) \_ 전자(electron) 핵(nucleus) \_ 양성자(proton) 중성자(neutron)

- 원자구조의 예

### ■ 반도체(semiconductor)

- 반도체에 사용되는 원자주기표

| 3가(p형) 원자                 | 4가(진성) 원자                  | 5가(n형) 원자                   | 전자 개수       |

|---------------------------|----------------------------|-----------------------------|-------------|

| <b>B</b> (Boron), 5번      | <b>C</b> (Carbon), 6번      | <b>N</b> (Nitrogen), 7번     | 2           |

| <b>Al</b> (Aluminum), 13번 | <b>Si</b> (Silicon), 14번   | <b>P</b> (Phosphorous), 15번 | 2, 8, -     |

| <b>Ga</b> (Gallium), 31번  | <b>Ge</b> (Germanium), 32번 | <b>As</b> (Arsenic), 33번    | 2, 8, 18, - |

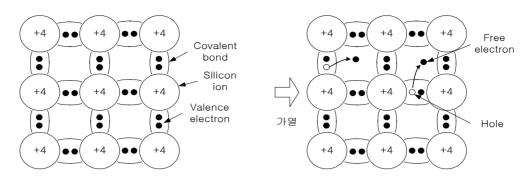

- 진성(intrinsic 또는 pure) 반도체: 최외각 전자가 4개(4가)인 원자(예, Si 및 Ge)

- → 4개의 가전자(valence electron)가 있으나 공유결합(covalent bond)으로 원자핵 과 강하게 결합되어 전도에 기여할 전자가 거의 없음(절연체에 가까움)

- 진성반도체에 열이 가해지면 일부 전자들이 공유결합으로부터 분리되어 자유전자 가 됨. 자유전자의 빈자리가 정공(hole)임. → 전도에 기여

자유전자농도 n = 정공농도 p = 진성농도  $n_i$  (온도의 함수)

<진성반도체의 원자구성> <진성반도체에 열이 가해지면 전자 및 정공발생>

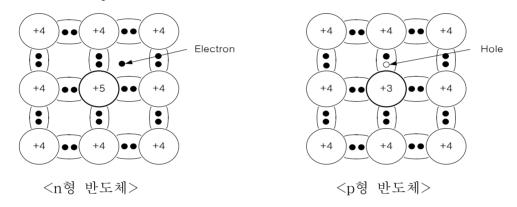

- 도핑 반도체: 진성반도체에 외인성(extrinsic 또는 unpure)물질을 첨가하여 만든 p형 또는 n형 반도체

- i) n형 반도체: 진성반도체에 5가의 외인성 물질(donor원자)을 도핑 다수캐리어가 전자, 소수캐리어가 정공

- ii) p형 반도체: 진성반도체에 3가의 외인성 물질(acceptor원자)을 도핑 다수캐리어가 정공, 소수캐리어가 전자

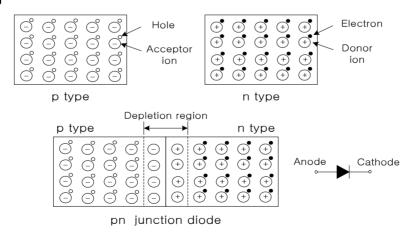

### ■ pn 접합

- 2 -

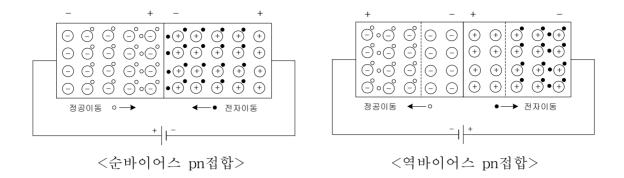

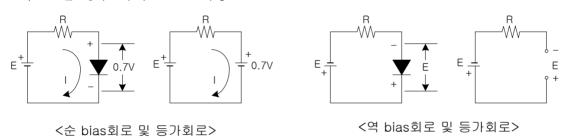

## ■ pn 접합

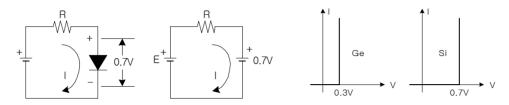

- Si 다이오드의 순바이어스 전압강하: 0.6~0.7V (보통 0.7V로 가정)

- Ge 다이오드의 순바이어스 전압강하: 보통 0.3V로 가정

- 역bias일 경우 다이오드는 개방

- 예제 2-1, 2-2, 2-3

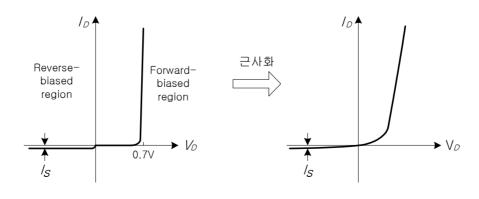

## ■ 다이오드 전류방정식

- 다이오드에 인가하는 전압에 따른 전류의 관계식

$$I_D = I_s \left( e^{V_D/\eta V_T} - 1 \right)$$

여기서,  $I_D$ = 다이오드전류[A],  $V_D$ = 다이오드전압[V],  $I_s$ = 포화(saturation)전류[A],  $\eta$  = 방사(emission)계수,  $1 \le \eta \le 2$  (Si: 2, Ge: 1),  $V_T =$  열적(thermal)전압  $= \frac{kT}{q} = \frac{T}{11,600}$  (실온도  $300^{\circ}$ K일 때 약 26mV)

- 예제 2-4, 2-5

# Chap. 3 The diode as a circuit element

## ■ 다이오드가 포함된 dc 희로의 해석

- 다이오드의 회로모델

- 예제 3-2, 3-3, 3-4: 순방향 bias일 때 dc전원(0.7V)으로 대치하여 회로해석

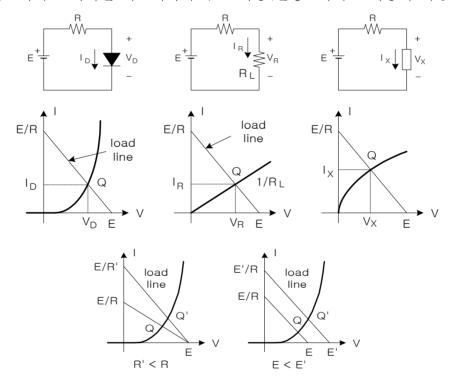

## □ 부하선(load line)

- 비선형소자의 도식적인 회로해석에 주로 사용(선형소자에도 적용이 가능)

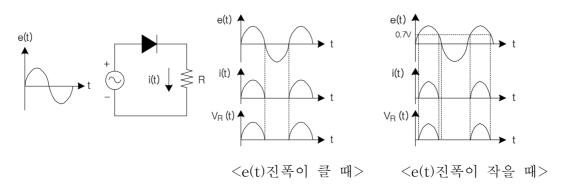

## □ 반파 정류기 (Half-wave rectifier)

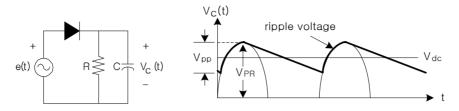

## □ 용량성 필터링

- 정류된 신호의 리플을 줄여 평활화시키기 위해 커패시터 필터를 사용함

- 리플율(ripple factor):

$$r = \frac{V_{pp}}{V_{dc}} \times 100\%$$

→ 리플율이 0일 때 이상적인 dc 전압

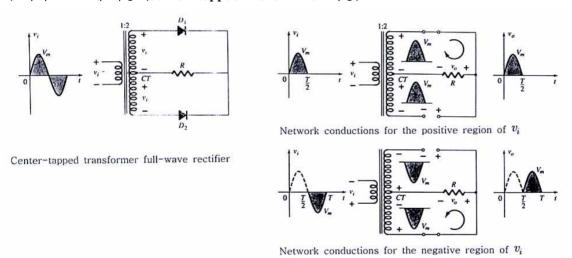

# □ 전파 정류기 (Full-wave rectifier)

# 1) 다이오드 2개 사용 (center-tapped transformer 사용)

# 2) 다이오드 4개 사용 (Bridge회로 사용)

Conduction path for the negative region of  $v_i$

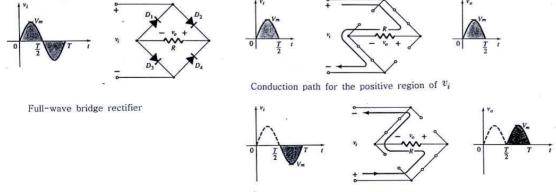

# Chap. 4 Bipolar junction transistors

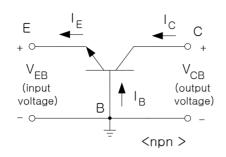

## ■ BJT동작 이론

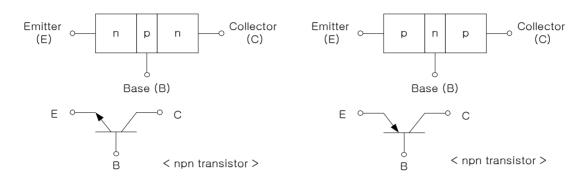

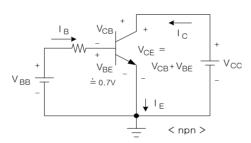

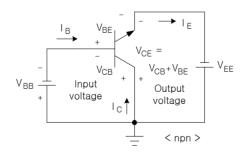

- BJT: 2개의 pn접합을 가진 3단자 반도체소자

- 이미터(E)-베이스(B) 접합이 순바이어스일 때: 이미터의 다수캐리어인 전자가 베이스로 확산, 베이스의 정공(소량)은 이미터로 확산(diffusion)

- 베이스(B)-컬렉터(C) 접합이 역바이어스일 때: 베이스의 소수캐리어(전자)가 컬렉터로 드리프트(drift)

- ▶ BJT의 일반적 바이어스: E-B접합은 순바이어스, B-C접합은 역바이어스

- 이미터의 다수캐리어는 베이스로 확산되고, 베이스로 확산된 캐리어(베이스에서 는 소수캐리어)는 전계에 의해 컬렉터로 드리프트됨

- npn 및 pnp의 키르히호프 전류관계식:  $I_E = I_C + I_B$

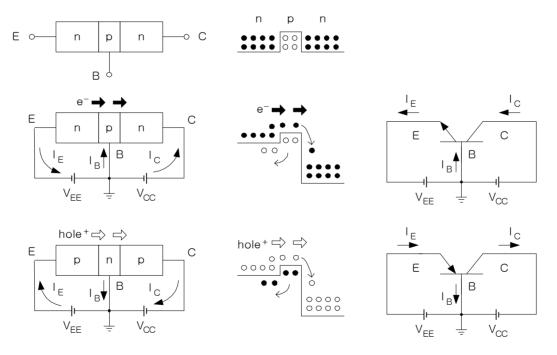

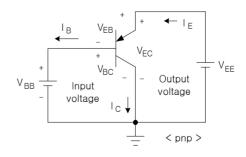

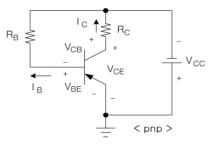

## ■ 공통-베이스(Common-Base) 특성

- 공통-베이스(CB) 트랜지스터: 입력단은 이미터(E), 출력단은 컬렉터(C)

- 이미터전류와 출력컬렉터전류 관계:

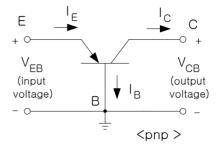

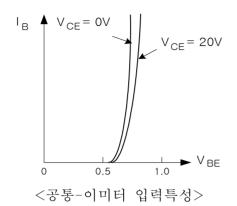

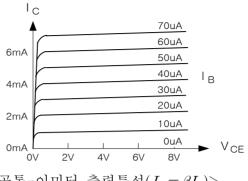

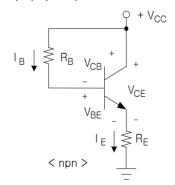

## ■ 공통-이미터(Common-Emitter) 특성

- 공통-이미터(CE) 트랜지스터: 입력단은 베이스(B), 출력단은 컬렉터(C) → 가장 많이 사용

- CE의 바이어스 배열: B-E는 순바이어스, C-B는 역바이어스( $V_{CB} = V_{CC} V_{BB}$ )  $\rightarrow$  증폭기로서의 바이어스 배열

- 베이스전류와 컬렉터전류 관계:

$$\begin{split} I_C &= \alpha I_E = \alpha (I_B + I_C) \\ &\frac{(1-\alpha)}{\alpha} I_C = I_B \quad \text{E.L.} \quad I_C \left(\frac{1}{\alpha} - 1\right) = I_B \quad \rightarrow \quad I_C = \frac{\alpha}{1-\alpha} I_B = \beta I_B \\ & I_C = \beta I_B, \quad \beta = \frac{\alpha}{1-\alpha} \;, \quad \alpha = \frac{\beta}{\beta+1} \end{split}$$

# ■ 공통-이미터 입력 및 출력특성

<공통-이미터 출력특성 $(I_{C}=eta I_{B})>$

## □ 트랜지스터 동작모드

| 모드(mode)       | E-B 바이어스 | C-B 바이어스 | 특 징                   | <u> </u>     |

|----------------|----------|----------|-----------------------|--------------|

| 활성(active)     | 순바이어스    | 역바이어스    | $V_{BE} = 0.7 V$      | 증폭기          |

| 포화(saturation) | 순바이어스    | 순바이어스    | $V_{C\!E} = 0.2V$     | 디지털(S/W=ON)  |

| 차단(cutoff)     | 역바이어스    | 역바이어스    | $I_E = I_B = I_C = 0$ | 디지털(S/W=OFF) |

<공통-이미터 활성모드 바이어스>

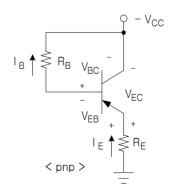

## ■ 공통-컬렉터(Common-Collector) 특성

- 공통-컬렉터(CC) 트랜지스터: 입력단은 베이스(B), 출력단은 이미터(E)

## ■ 바이어스(bias)회로

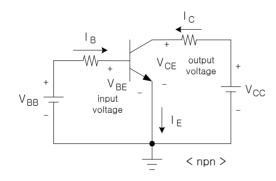

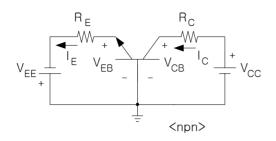

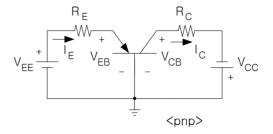

## ■ 공통-베이스 바이어스회로

▶ npn CB 바이어스회로의 해석방법

$$\begin{split} V_{BE} &= 0.7 \, V \, (S\!i), \; 0.3 \, V \, (G\!e) \\ I_E &= (V_{E\!E} - V_{E\!B}) / R_E \\ I_E &\approx I_C \\ V_{C\!B} &= V_{C\!C} - I_C R_C \end{split}$$

→ 예제 4-9

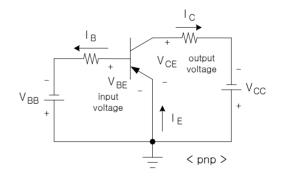

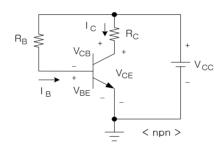

## ■ 공통-이미터 바이어스회로

▶ npn CE 바이어스회로의 해석방법

$$\begin{split} V_{BE} &= 0.7 \, V(S\!i), \; 0.3 \, V(G\!e) \\ I_{B} &= (V_{C\!C} \!- V_{B\!E}) / R_{B} \\ I_{C} &= \beta I_{B} \\ V_{C\!E} &= V_{C\!C} \!- I_{C} R_{C} \end{split}$$

→ 예제 4-10

### ■ 공통-컬렉터 바이어스회로

## ▶ npn CC 바이어스회로의 해석방법

$$V_{BE} = 0.7 \, V(Si), \; 0.3 \, V(Ge)$$

$$I_B = \frac{V_{CC} - V_{BE}}{R_B + (\beta + 1) R_E}$$

$$I_E = (\beta + 1) \, I_B \approx I_C$$

$V_{CE} = V_{CC} - I_E \, R_E$   $\rightarrow$  예제 4-12

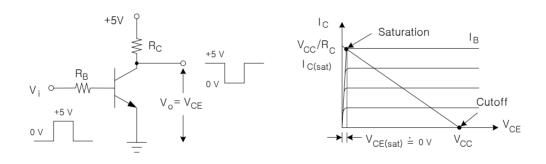

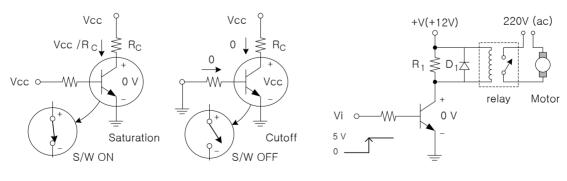

## ■ BJT인버터(트랜지스터 스위치)

- 트랜지스터는 디지털 논리회로와 스위칭회로로도 널리 사용

- 트랜지스터 인버터(또는 스위치)

| 입력         | BJT 모드         | 출력         |

|------------|----------------|------------|

| low (OV)   | 차단(cutoff)     | high (+5V) |

| high (+5V) | 포화(saturation) | low (≈0V)  |

• 포화일 때:

$$I_{C(sat)}=V_{CC}/R_C$$

,

$$I_{B(sat)}=I_{C(sat)}/\beta=V_{CC}/(\beta R_C)$$

$\rightarrow$  예제 4-16

## ■ 스위치로서의 트랜지스터

<BJT의 스위치 ON> <BJT의 스위치 ON>

<BJT에 의한 릴레이제어>

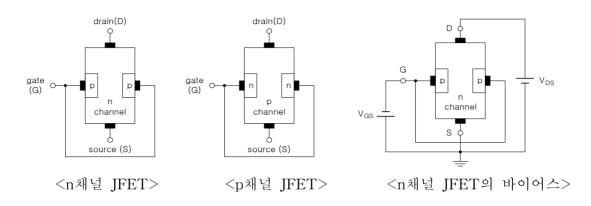

# Chap. 5 Field-Effect Transistors

### ■ JFET

- JFET의 분류: n채널 및 p채널 JFET

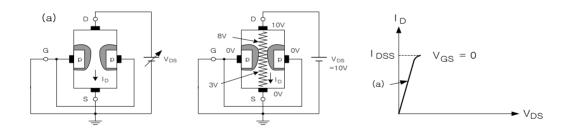

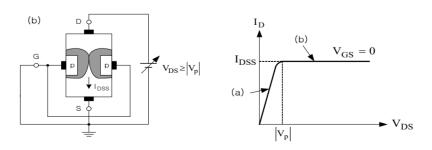

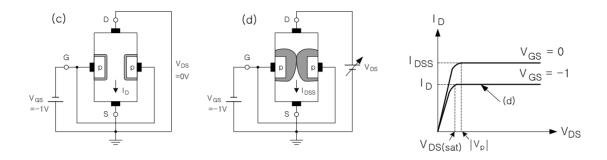

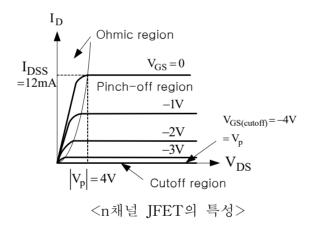

## ▶ n채널 JFET의 드레인 특성

- (a)  $V_{GS}=0$  V일 때  $V_{DS}$ 의 증가에 따라 드레인(D)에서 소스(S)로 흐르는 전류  $I_D$ 는 선형적으로 증가(n채널의 저항성으로 인함)

- $ightarrow V_{DS}$ 가 증가하면 게이트 G와 드레인 D(또는 채널)사이에 공핍영역이 증가하여 드레인과 소스 사이의 채널폭이 좁아짐.

- (b)  $V_{DS}$ 가  $V_P$ (pinch-off voltage)일 때 채널폭이 최대한 좁아져서 통과하는 전류 량을 제한함.

- $\rightarrow$   $V_{DS}$ 가  $V_P$ 보다 더욱 증가하여도 채널폭은 완전히 0이 되지 못하며  $I_D$ 는 일 정하게 유지됨. 이때의 전류를 포화전류(saturation current)  $I_{DSS}$ 라 함.

- (c)  $V_{GS} = -1V$ 일 때 게이트와 채널은 역바이어스되어 공핍영역이 발생함.

- (d)  $V_{DS}$ 가 증가함에 따라 채널폭은 좁아지며  $V_{GS} = 0\,V$ 일 때 보다 빨리 채널이 포화됨.  $\to$  포화전압  $V_{DS(sat)}$ 는 보다 적으며, 포화전류  $I_D$ 도  $I_{DSS}$ 보다 적음.

- (e)  $V_{GS} = -2\,V, \, -3\,V, \, -4\,V$ 일 때를 포함한 전체의 특성곡선: 그림 5-6

- · 선형영역을 voltage-controlled-resistance 또는 ohmic region이라 함

- · 수평영역을 pinch-off, active 또는 saturation region이라 함(증폭에 사용)

- $\cdot I_D = 0$ 인 수평영역을 cutoff region이라 함

- \* 차단(cutoff)영역에서의  $V_{GS(cutoff)}$ 는  $V_P$ 와 같음.  $V_{GS(cutoff)} = V_P$

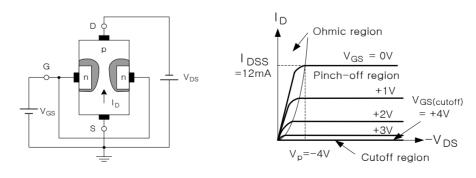

▶ p채널 JFET의 구성 및 드레인 특성

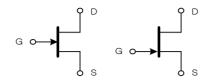

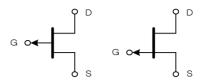

## - JFET의 기호

<n 채널 JFET의 기호>

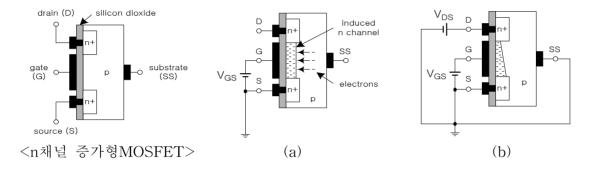

#### ■ MOS(Metal-Oxide-Semiconductor)FET

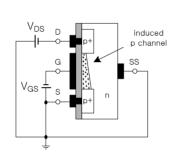

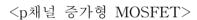

ㅁ 증가형(Enhancement type) MOSFET

- (a)  $V_{CS}$ 만 인가,  $V_{DS}$ 는 인가하지 않음

- $V_{CS}$ 가 증가하면 전자가 게이트(G)로 모여 n채널이 형성

- → 드레인(D)과 소스(S)간의 전하이동 통로를 형성

- 경계전압(threshold voltage)  $V_T$ : n채널이 처음으로 형성되기 시작하는 게이트 전압  $V_{CS}$ 이며 일반적으로  $1{\sim}3$ V정도임

- (b)  $V_{CS}$  및  $V_{DS}$ 를 모두 인가

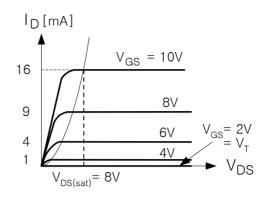

- $V_{DS}$ 가 작을 때:  $V_{DS}$ 가 증가함에 따라  $\mathbf{n}$ 채널의 저항성으로 인해 전류가 선형적으로 증가

- $V_{DS}$ 가 클 때: 드레인부근의 채널폭이 좁아져서 채널을 통해 흐르는 전류는 일정 하게 유지

- \* 채널폭 감소원인:  $V_{DS}$ 가 증가할수록  $V_{GD}$ 는 작아지므로 드레인부근의 채널 폭이 좁아짐

- 예)  $V_{GS}=10\,V,~V_{DS}=3\,V$ 이면  $V_{GD}=10\,V-3\,V=7\,V$   $V_{DS}=4\,V$ 이면  $V_{GD}=10\,V-4\,V=6\,V$ 이면

- ightarrow  $V_{GS}$ 가 최소  $V_{T}$ (예,  $2\mathrm{V}$ )이상이 되어야 채널이 형성됨

- 포화전압:  $V_{DS(sat)} = V_{GS} - V_T$  (예,  $10\,V - 2\,V = 8\,V$ )

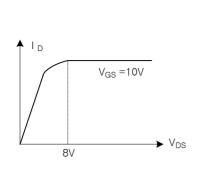

<드레인 특성>

- 증가형 MOSFET의 기호

<n채널 증가형 MOSFET>

<p채널 증가형 MOSFET>

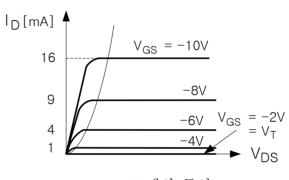

# Chap. 6 Amplifier characteristics

## ■ 증폭기 특성

- 증폭기의 성능평가 항목

- 입력저항(input resistance) → 클수록 좋음

- 전압이득(voltage gain) → 클수록 좋음

- 전류이득(current gain) → 클수록 좋음

- 출력저항(output resistance) → 작을수록 좋음

- 전력이득(power gain) → 클수록 좋음

- □ 입력저항: 입력단에서의 총 저항 즉, 입력전원에서 본 저항

- 입력저항:  $r_i = v_i/i_i$

- □ 전압이득: 입력전압과 출력전압의 비

- 전압이득:  $A_v \equiv \frac{v_o}{v_i}$   $(v_o$ 는 무부하시 즉, 출력단 개방시의 출력전압)

- □ 전류이득: 입력전류와 출력전류의 비

- 전류이득:  $A_i \equiv \frac{i_o}{i_i}$   $(i_o$ 는 출력단을 단락했을 때의 전류임)

- □ 출력저항: 출력에서 본 저항

- 출력단에 외부전압 $(v_{ext})$ 을 인가하고 유입되는 전류 $(i_{ext})$ 조사:  $r_o \equiv v_{ext}/i_{ext}$

- 출력단 좌측의 테브닌등가회로의 저항:  $r_o \equiv v_{oc}/i_{sc}$

- □ 전력이득: 입력전력과 출력전력의 비

- 전력이득:  $A_p \equiv \frac{p_o}{p_i} = \frac{v_o i_o}{v_i i_i} = A_v A_i$

- □ 전압이득공식

- 부하가 있을 때의 전압이득:  $A_v \equiv \frac{v_L}{v_i} = \frac{-i_o R_L}{i_i r_i} = -A_i \frac{R_L}{r_i}$

# Chap. 7 Small-Signal Transistor Amplifier

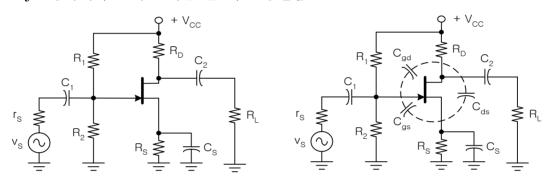

### ■ 서언

- 단일 BIT 및 FET 소신호증폭기의 동작 및 특성을 공부

- BJT증폭기: CE(common emitter), CB(common base), CC(common collector)

- FET증폭기: CS(common source), CG(common gate), CD(common drain)

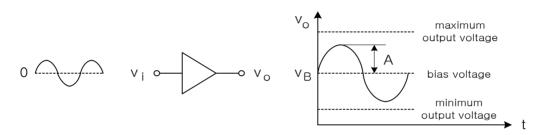

#### □ 바이어스의 목적

- 바이어스의 목적: 출력할 수 있는 총 영역의 중간에 dc출력레벨을 두어 ac파형을 이에 중첩되게 함.

- 출력전압:  $v_o(t) = V_B + A \sin \omega t$   $\rightarrow V_B$ 가 dc성분으로 바이어스전압임

- 바이어스전압이 적절하지 못하면 출력파형이 클리핑(clipping)되어 왜곡됨

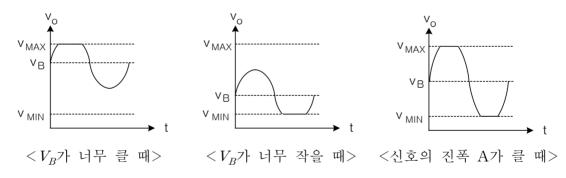

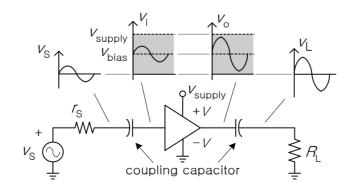

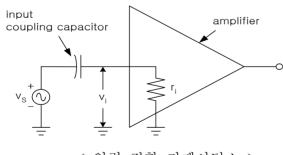

## □ 결합 커패시터(coupling capacitor)

- 증폭기의 입력 또는 출력단에 dc전류는 차단(blocking)하고 ac전류만 전달하기 위해서 결합커패시터를 사용 (ac결합, dc차단)

- → blocking capacitor라고도 부름

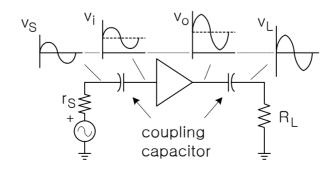

## ■ 소신호모델을 사용한 증폭기의 해석

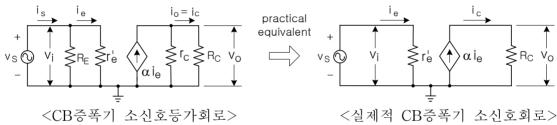

## □ CB증폭기의 소신호모델

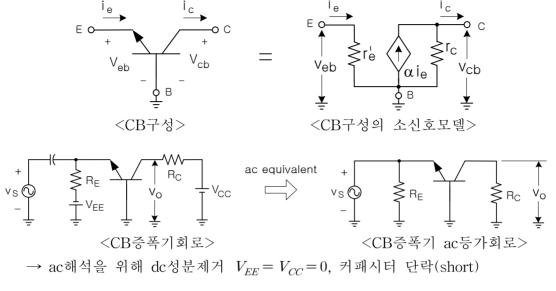

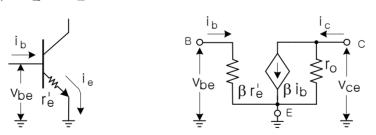

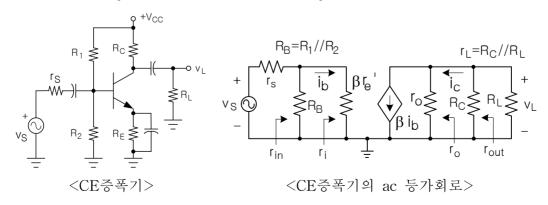

## □ CE증폭기의 소신호모델

<CE구성 BJT의 입력회로> <CE구성 BJT의 근사적 소신호모델>

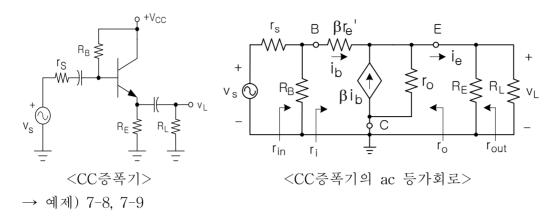

# □ CC증폭기의 소신호모델

# ※ BJT증폭기의 특성비교

|            | СВ      | CE     | CC       | CE with $R_E$ |

|------------|---------|--------|----------|---------------|

| 전압이득 $A_v$ | 대 (비반전) | 대 (반전) | ≈1 (비반전) | 중 (반전)        |

| 전류이득 $A_i$ | ≈ 1     | 대      | 대        | 대             |

| 전력이득 $A_p$ | 중       | 대      | 소        | 대             |

| 입력저항 $r_i$ | 소       | 중      | 대        | 대             |

| 출력저항 $r_o$ | 대       | 중      | 소        | 대             |

|            | 단독사용 않음 |        | 버퍼로 이용   |               |

# ■ JFET 증폭기의 소신호해석

※ BJT 및 JFET 증폭기구성들의 유사성

|      | 증폭기의 종류                                                                       |                                                        |                                                               |

|------|-------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|

| ВЈТ  | CE                                                                            | CC                                                     | СВ                                                            |

| JFET | CS                                                                            | CD                                                     | CG                                                            |

| 특성   | $A_v$ : 대(-), $A_i$ : 대 $R_i$ : BJT 중, JFET $\infty$ , $R_o$ : 중단일증폭기에서 주로 사용 | $A_vpprox 1,\; A_i$ : 대 $R_i$ : 대, $R_o$ : 소<br>버퍼로 사용 | $A_v$ : 대(+), $A_ipprox 1$ $R_i$ : 소, $R_o$ : 대<br>단독으로 사용 않음 |

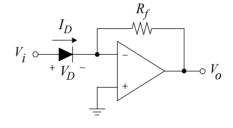

# Chap. 8 Ideal Operational Amplifier Circuits and Analysis

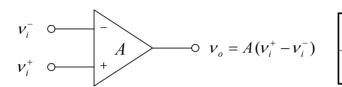

## ■ 이상적 연산증폭기(operational amplifier; OP amp)

- 이상적 OP amp의 구조

- 두 개의 차동 입력과 한 개의 출력을 가지는 직결(direct-coupled) 증폭기

- 두 개의 전원공급기(접지에 대해 +V 및 -V)

| $v_i^- = 0$ (접지) | $v_o = A v_i^+$ (비반전) |

|------------------|-----------------------|

| $v_i^+=0$ (접지)   | $v_o = -Av_i^-$ (반전)  |

- 이상적 OP amp의 특성

- ① 무한대의 이득

- ③ 영의 출력임피던스

- ② 무한대의 입력임피던스

- ④ 무한대의 주파수대역

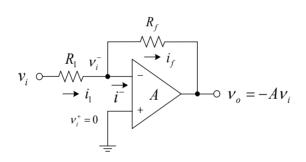

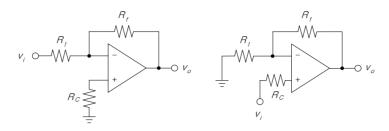

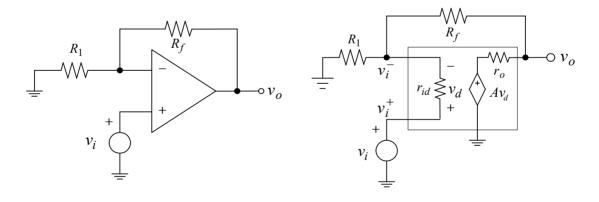

## □ 반전 증폭기

- $v_i^+=0$ 이므로  $v_o=-Av_i^-$  또는  $v_i^-=-v_o/A$

- ※ 이상적인 OP amp는 이득 A가 무한대이므로  $v_i^-=0$  (virtual ground)

\*\* 이상적인 OP amp는 입력임피던스가 무한대이므로  $i^-=0$

•

$$i_1=i_f$$

이므로  $\frac{v_i-v_i^-}{R_1}=\frac{v_i^--v_o}{R_f}$

•

$$v_i^-=0$$

이므로  $\frac{v_i}{R_1}=\frac{-v_o}{R_f}$  또는  $\frac{v_o}{v_i}=\frac{-R_f}{R_1}$

→ 예제 8-1

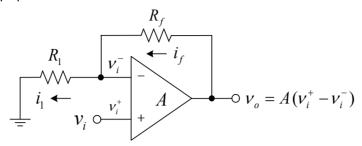

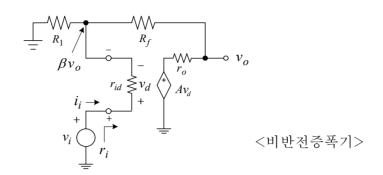

#### □ 비반전 증폭기

•

$$i_1 = i_f$$

이므로  $\frac{v_i^-}{R_1} = \frac{v_o - v_i^-}{R_f}$  (\*)

•

$$v_i^- = v_i^+ = v_i$$

이므로 식(\*)는  $\frac{v_i}{R_1} = \frac{v_o - v_i}{R_f}$  또는

$$\frac{v_o}{v_i} = \frac{R_1 + R_f}{R_1} = 1 + \frac{R_f}{R_1}$$

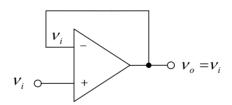

## □ 전압폴로워(voltage follower)

- 비반전 증폭기에서  $R_f=0$  및  $R_i=\infty$ 이므로  $\dfrac{v_o}{v_i}=1$  또는  $v_o=v_i$

- 버퍼(buffer)로 이용 (높은 입력임피던스, 낮은 출력임피던스)

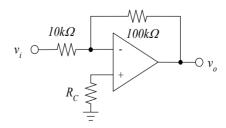

## $\square$ 보상저항 $R_{a}$

- OP amp가 이상적이 아닐 경우 적은 입력전류(입력 바이어스전류)가 흐름 이로 인해 입력이 0임에도 적은 dc 출력전압(출력 오프셑전압)이 발생

- ightarrow 이를 보상하기위해 다음과 같이 보상저항  $R_{C}$ 를 연결

- 반전 증폭기의 경우:  $R_C = R_f \parallel (r_S + R_1)$  (여기서  $r_S$ 는 전원저항)

- 비반전 증폭기의 경우:  $R_C = (R_f \parallel R_1) r_S$

- ▶ 보상저항값은 10장에서 유도

<보상저항을 사용한 반전 및 비반전 증폭기>

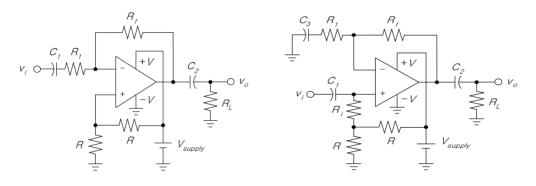

## □ 단일 전원 동작

- OP amp는 2개의 전원공급단자가 있으나 1개의 전원공급만으로도 동작 가능

- -V단자를 접지시키고, +V단자에만 전원을 공급

- 양의 전압에서 선형동작이 되도록 입력신호는 dc 바이어스되어야 함

- 출력신호는 dc 전압을 포함하여 출력됨

- 입력 및 출력단에 커패시터 결합이 요구됨

- +입력단에 전압분배기에 의해 바이어스전압을 인가함

- 비반전증폭기에서  $R_i$ 는  $v_i$ 에서 본 입력저항을 높이는데 사용될 수 있음

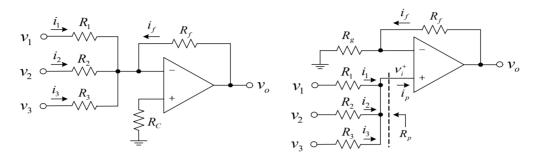

# ■ 전압 가산, 감산 및 스케일링

## □ 전압 가산 (voltage summation)

- (1) 반전 증폭기의 경우

- OP amp가 이상적일 때  $i_1 + i_2 + i_3 = -i_f$

$$\bullet \quad \frac{v_1}{R_1} + \frac{v_2}{R_2} + \frac{v_3}{R_3} = \frac{-v_o}{R_f} \quad \Xi \sqsubseteq \quad v_o \! = \! - \! \left( \frac{R_f}{R_1} v_1 + \frac{R_f}{R_2} v_2 + \frac{R_f}{R_3} v_3 \right)$$

•

$$R_1 = R_2 = R_3 = R \circ \mathbb{R}$$

$v_o = -\frac{R_f}{R} (v_1 + v_2 + v_3)$

•

$$R_f = R \circ \exists v_o = -(v_1 + v_2 + v_3)$$

• 보상저항

$$R_C = R_f \parallel R_1 \parallel R_2 \parallel R_3$$

- (2) 비반전 증폭기의 경우

- $R_p \mid_{v_1 = v_2 = v_3 = 0} = R_1 \parallel R_2 \parallel R_3$

$$\bullet \quad i_p \mid {}_{v_i^+ = 0} = i_1 + i_2 + i_3 = \frac{v_1}{R_1} + \frac{v_2}{R_2} + \frac{v_3}{R_3}$$

•

$$v_i^+ = R_p \cdot i_p$$

$$\begin{array}{ll} \bullet & v_o = \left(1 + \frac{R_f}{R_g}\right) \! v_i^+ = \! \left(1 + \frac{R_f}{R_g}\right) \! \left(\frac{R_p}{R_1} v_1 + \frac{R_p}{R_2} v_2 + \frac{R_p}{R_3} v_3\right) \\ & \rightarrow & \text{ all } 8\text{-}3 \end{array}$$

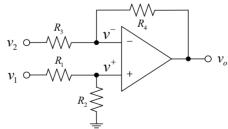

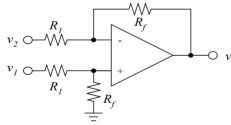

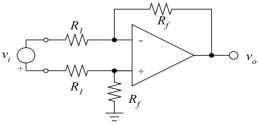

# □ 전압 감산 (voltage subtraction)

- 중첩정리를 사용하여 먼저  $v_2=0$ 이라 두면  $v^+=\frac{R_2}{R_1+R_2}v_1$ 이므로  $v_{o1}=\left(1+\frac{R_4}{R_2}\right)\!v^+=\left(1+\frac{R_4}{R_2}\right)\!\left(\frac{R_2}{R_1+R_2}\right)\!v_1$

- $v_1=0$ 이라 두면  $v^+=0$ 이므로 반전증폭기로 동작하여  $v_{o2}=-\frac{R_4}{R_3}v_2$

• 두 입력이 동시에 인가되면

$$v_{o1}+v_{02}=\left(1+rac{R_4}{R_3}\right)\left(rac{R_2}{R_1+R_2}\right)v_1-\left(rac{R_4}{R_3}\right)v_2$$

•

$$R_1=R_3=R$$

이고  $R_2=R_4=AR$ 이면  $v_o=A\left(v_1-v_2\right)$   $\rightarrow$  예제 8-4

## ■ 제어 전압원 및 전류원

- OP amp를 사용한 전압원 및 전류원

## □ 전압제어 전압원(voltage-controlled voltage source; VCVS)

- 이상적 VCVS의 요건

- ① 출력전압은 제어(입력)전압의 상수(k) 배,  $V_o = k V_i$

- ② 출력전압이 부하로 끌어내는 전류와는 무관하게 일정

- OP amp를 이용한 반전 및 비반전 증폭기가 전압제어 전압원임

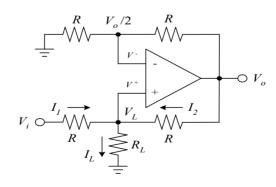

## □ 전압제어 전류원(voltage-controlled current source; VCCS)

- 이상적 VCCS의 요건

- ① 출력전류는 제어(입력)전압의 상수(k) 배,  $I_L = k \, V_i$

- ② 출력전류가 부하  $R_L$ 에 무관하게 일정

- 접지된 부하에 동작할 수 있는 VCCS 회로

• KCL에 의해  $I_L = I_1 + I_2$  또는  $I_L = \frac{V_i - V_L}{R} + \frac{V_o - V_L}{R}$

- 전압분배 동작으로  $V^- = \left(\frac{R}{R+R}\right)V_o = V_o/2$

- $V^-=V^+=V_L=V_o/2$ 이므로  $I_L=rac{V_i}{R}-rac{V_o}{2R}+rac{V_o}{R}-rac{V_o}{2R}=rac{V_i}{R}$

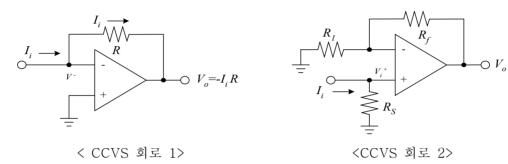

# □ 전류제어 전압원(current-controlled voltage source; CCVS)

- 이상적 CCVS의 요건

- ① 출력전압은 제어(입력) 독립전류 크기의 상수(k) 배,  $V_o = k I_i$

- ② 출력에 연결되는 부하에 무관

- (1) CCVS 회로 1

- $V^-$ 는 가상접지이므로  $V_o = -I_i R$

- (2) CCVS 회로 2

•

$$V^+ = I_i R_S$$

이므로  $V_o = \left(1 + \frac{R_f}{R_1}\right) V_i^+ = \left(1 + \frac{R_f}{R_1}\right) R_S I_i$

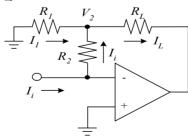

# □ 전류제어 전류원(current-controlled current source; CCCS)

- 이상적 CCCS의 요건

- ① 출력전류는 제어(입력) 독립전류 크기의 상수(k) 배,  $I_L = kI_i$

- ② 출력전류는 부하에 무관

- $V_2 = -I_i R_2$ 이므로  $I_1 = (0 V_2)/R_1 = I_i R_2/R_1$  KCL에 의해  $I_L = I_1 + I_i$  이므로  $I_L = \frac{R_2}{R_1} I_i + I_i = \left(\frac{R_2}{R_1} + 1\right) I_i$

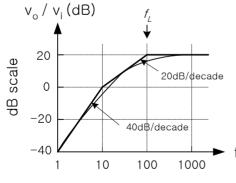

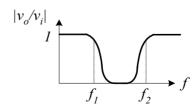

# Chap. 9 Frequency Response

## ■ 정의 및 기본 개념

- 주파수응답(frequency response)

- 입력신호의 주파수 변화에 따른 출력신호의 진폭(또는 실효값) 변화

- 출력신호는 진폭뿐만 아니라 위상각(phase angle)도 변화함

- → 입력의 주파수변화에 따른 출력의 위상이동(phase shift)을 위상응답(phase response)이라 함

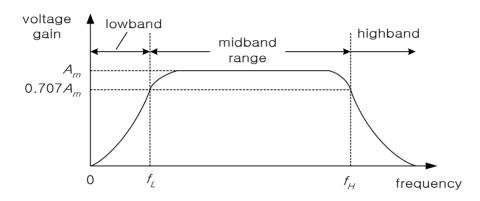

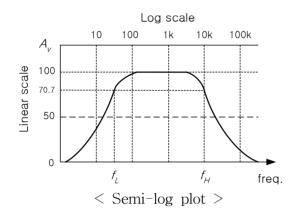

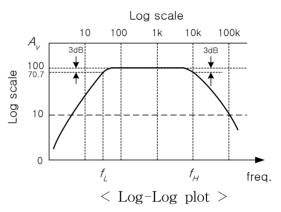

- 증폭기의 전형적인 주파수응답(frequency response)

- 하측 차단주파수(lower cutoff frequency)  $f_L$  : 이득이 중간대역(midband)이득  $A_m$ 보다  $1/\sqrt{2}\approx 0.707$ 배가 되는 낮은 대역에서의 주파수

- 상측 차단주파수(upper cutoff frequency)  $f_H$  : 이득이  $0.707\,A_m$ 일 때의 높은 대역에서의 주파수

- 주파수대역(bandwidth) :  $BW = f_H f_L$

- 중간대역에서의 출력 전력(power) : 출력단 부하저항 R양단의 전압이  $v({

m rms})$  일 때  $P_{(midband)} = v^2/R \; [W]$

- 차단주파수 $(f_L$  및  $f_H$ )에서의 출력 전력(power) :

$$P_{(cutoff)} = \left(\frac{\sqrt{2}}{2}v\right)^2 / R = 0.5 \frac{v^2}{R} = 0.5 P_{(midband)} [W]$$

$ightarrow f_L$  및  $f_H$ 일 때의 전력은 중간대역에서 전력의 반이므로 차단주파수를 반전력주파수(half-power frequency)라고도 함

- 예제 9-1)

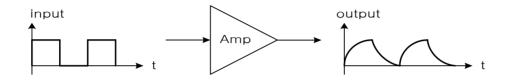

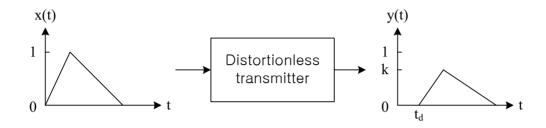

## ㅁ 진폭 및 위상 왜곡(distortion)

- 주파수응답(진폭 및 위상)이 일정하지 않으면 출력파형이 왜곡이 됨

- 입력파형에 포함된 모든 주파수성분들의 주파수응답이 모두 균일하여야 출력파 형이 왜곡되지 않음

- 예) 입력이 구형파일 때 무한 고조파(harmonics)의 주파수가 포함되고, 증폭기의 고주파응답이 감쇄하면 높은 고조파성분이 감쇄되어 출력파형은 왜곡이 됨

#### ■ 데시벨(Decibel) 및 로그선도

#### ㅁ 데시벨(Decibel; dB)

- 주파수응답의 데이터는 주로 데시벨로 표현됨

- dB 전력이득:  $dB = 10\log_{10}\left(\frac{P_2}{P_1}\right)$  (여기서,  $P_1$  및  $P_2$ 는 입력 및 출력의 전력)

- $dB=10\log_{10}\!\left(\frac{v_2^2/R_2}{v_1^2/R_1}\right)$  :  $R_1$  및  $R_2$  양단의 전력 비

- $R_1 = R_2 = R$   $\stackrel{\bigcirc}{=}$   $\stackrel{\square}{=}$   $dB = 10 \log_{10}\!\left(\frac{v_2^2/R}{v_1^2/R}\right) = 10 \log_{10}\!\left(\frac{v_2}{v_1}\right)^2 = 20 \log_{10}\!\left(\frac{v_2}{v_1}\right)$

- dB 전압이득:  $dB(voltage~gain) = 20\log_{10}\left(\frac{v_2}{v_1}\right)$

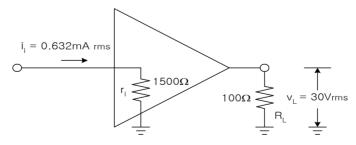

예제 9.2) 전력이득 및 전압이득의 dB 표현?

① dB 전력이득:

$$10\log_{10}\left(\frac{P_L}{P_i}\right) = 10\log_{10}\left(\frac{v_L^2/R_L}{i_i^2r_i}\right) = 10\log_{10}\left(\frac{9\,W}{0.6\times10^{-3}\,W}\right) = 41.76~dB$$

② dB 전압이득:

$$20\log_{10}\left(\frac{v_L}{v_i}\right) = 20\log_{10}\left(\frac{v_L}{i_ir_i}\right) = 20\log_{10}\left(\frac{30}{0.948}\right) = 30~dB$$

|   | $(v_2/v_1)$ | $dB = 20log_{10}(v_2/v_1)$ | $(v_2/v_1)$ | $dB = 20 log_{10}(v_2/v_1)$ |

|---|-------------|----------------------------|-------------|-----------------------------|

| Ī | 0.001       | -60                        | 10          | 20                          |

|   | 0.01        | -40                        | 100         | 40                          |

|   | 0.1         | -20                        | 1000        | 60                          |

|   | 1.0         | 0                          |             |                             |

## ㅁ 반 대수(Semilog) 및 대수-대수(Log-Log) 선도

- 반 대수 : 한 축은 대수(log)이고 다른 축은 선형눈금(linear scale)

- 대수-대수: 양 축 모두 대수눈금(log scale)

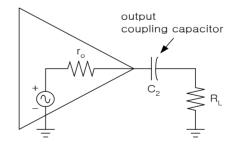

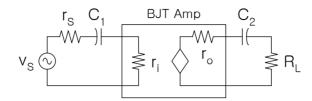

## ■ 직렬 커패시턴스 및 저주파수 응답

- 증폭기에서의 하측 차단주파수는 신호경로에 직렬로 연결된 커패시턴스에 영향을 받음

- $\rightarrow$  증폭기의 입력 및 출력 결합 커패시턴스가 이에 해당함  $(f_L)$ 에 직접 영향)

< 입력 결합 커패시턴스 >

< 출력 결합 커패시턴스 >

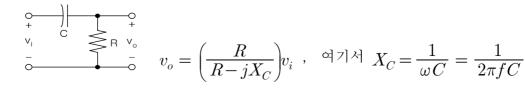

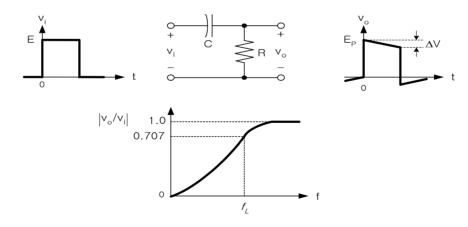

### □ 고역통과 RC회로망

$$|v_o| = \frac{R}{\sqrt{R^2 + X_C^2}} |v_i| = \frac{R}{\sqrt{R^2 + (1/\omega C)^2}} |v_i| = \frac{1}{\sqrt{1 + (1/\omega RC)^2}} |v_i|$$

$$\omega = 1/(RC)$$

이면,  $\mid v_o \mid = \frac{1}{\sqrt{1+1}} \mid v_i \mid = \frac{1}{\sqrt{2}} \mid v_i \mid = 0.707 \mid v_i \mid$

\*\* 하측 차단주파수:

$$\omega_L = \frac{1}{RC}$$

또는  $f_L = \frac{1}{2\pi RC}$

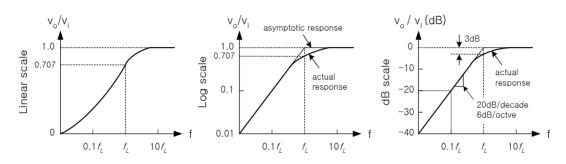

## ▶ 진폭 주파수특성

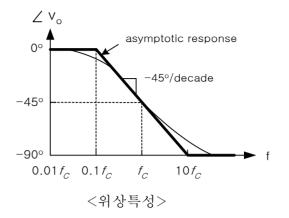

## ▶ 위상특성

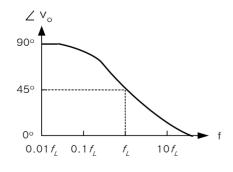

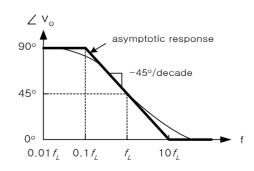

•  $v_i$ 의 위상을 0이라 두었을 때 $(\angle v_i = 0^o)$   $v_o$ 의 위상

$$\angle v_o = -tan^{-1} \left(\frac{-X_C}{R}\right) + \angle v_i = tan^{-1} \left(\frac{X_C}{R}\right) = tan^{-1} \left(\frac{1}{\omega RC}\right)$$

- $\omega = 1/RC = \omega_L($ 차단주파수)일 때  $\angle v_o = tan^{-1}(1) = 45^o$

- ightarrow 차단주파수에서  $v_{o}$ 의 위상은  $v_{i}$ 의 위상보다  $45^{\circ}$  앞섬(lead)

- 입력주파수 f에 따른 출력의 위상은  $\angle v_o = tan^{-1}(f_L/f)$

- ightarrow 입력주파수 f=0일 때 출력의 위상  $\angle v_o=90^o$   $f=\infty$ 일 때  $\angle v_o=0^o, \qquad f=f_L$ 일 때  $\angle v_o=45^o$

## 1) 입력 결합 커패시턴스가 있을 때의 주파수 응답

• 입력전압:

$$v_i=\left(\frac{r_i}{r_i-jX_{C_1}}\right)\!\!v_S$$

여기서  $X_{C_1}=\frac{1}{\omega C_1}=\frac{1}{2\pi fC_1}$

• 차단주파수:

$$\omega_L = \frac{1}{r_i C_1}$$

또는  $f_L = \frac{1}{2\pi r_i C_1}$

• 입력전압 진폭:

$$\mid v_i \mid \ = \frac{r_i}{\sqrt{r_i^2 + X_{C_1}^2}} \mid v_S \mid \ = \frac{r_1}{\sqrt{r_1^2 + (1/\omega \, C_1)^2}} \mid v_S \mid \ = \frac{1}{\sqrt{1 + (1/\omega r_i \, C_1)^2}} \mid v_S \mid$$

• 입력전압 위상:

$$\angle v_o = -\tan^{-1}\left(\frac{-X_C}{R}\right) + \angle v_i = \tan^{-1}\left(\frac{X_C}{R}\right) = \tan^{-1}\left(\frac{1}{\omega RC}\right)$$

## ightharpoonup 소스저항 $r_s$ 가 있는 경우

• 입력전압 진폭:

$$|v_i| = \left(\frac{r_i}{r_S + r_i}\right) \frac{1}{\sqrt{1 + \frac{1}{\omega(r_S + r_i)C_1^2}}} |v_S|$$

• 하측 차단주파수 즉,  $\mid v_i \mid / \mid v_S \mid = 0.707 \, r_i / (r_S + r_i )$ 이 되는 주파수:

$$\omega_L = \frac{1}{\left(r_i + r_S\right)C_1}$$

또는  $f_L = \frac{1}{2\pi\left(r_i + r_S\right)C_1}$

• 입력전압 위상:

$$\angle v_i \ = \ -\tan^{-1}\!\left(\frac{-X_{C_{\!\!1}}}{r_i+r_S}\right) + \ \angle v_S \ = \ \tan^{-1}\!\left(\frac{X_{C_{\!\!1}}}{r_i+r_S}\right) = \ \tan^{-1}\!\left(\frac{1}{\omega\left(r_i+r_S\right)C_1}\right)$$

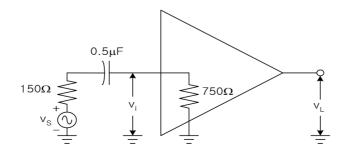

예제 9-5) 중간대역 증폭도  $\mid v_L \mid / \mid v_S \mid$  가 90인 증폭기.

① 중간대역에서의 전압이득  $\mid v_L \mid / \mid v_i \mid$  ?

- ② 하측 차단주파수 :  $f_L = \frac{1}{2\pi(150+750)(0.5\mu F)} = 354 Hz$

- ③ 하측 차단주파수에서의 dB 전압이득: 중간대역 dB 이득이  $20\log_{10}(90) = 39.1dB$ 이므로 차단 dB 이득은 3dB 아래 이므로 39.1 - 3 = 36.1dB (또는  $20\log_{10}(90/\sqrt{2}) = 36.1dB$ )

2) 출력 결합 커패시턴스가 있을 때의 주파수 응답

• 차단주파수 :

$$\omega_L = \frac{1}{(r_o + R_L)C_2}$$

또는  $f_L = \frac{1}{2\pi (r_o + R_L)C_2}$

3) 입력 및 출력 결합 커패시턴스가 모두 있을 때의 주파수 응답

- 입력 결합 커패시턴스에 의한 차단주파수 :  $f_1 = \frac{1}{2\pi (r_i + r_S)C_1}$

- 출력 결합 커패시턴스에 의한 차단주파수 :  $f_2 = \frac{1}{2\pi (r_o + R_L)C_2}$

- 전체의 차단주파수  $f_L$ 과의 관계:  $f_L^4-\left(f_1^{\;2}+f_2^{\;2}\right)f_L^{\;2}-f_1^{\;2}f_2^{\;2}=0$  (부록 C)  $\to f_1\ll f_2$  이면  $f_L\approx f_2$ ,  $f_1=f_2=f$  이면  $f_L=1.55f$

예)  $f_1 = 10 Hz$ 이고  $f_2 = 100 Hz$ 일 때의 주파수 특성

- ▶ 전체의 차단주파수  $f_L$ 은 100Hz와 유사함.

- ullet  $f_L = 100 {

m Hz}$ 일 때  $51^{

m o}$ ,  $f = 10 {

m Hz}$ 일 때  $129^{

m o}$ ,  $f = 0 {

m Hz}$ 일 때  $180^{

m o}$

→ 예제 9-7)

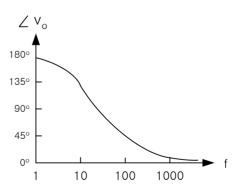

#### ■ 병렬 커패시턴스 및 고주파수 응답

- 증폭기에서의 상측 차단주파수는 신호경로와 접지사이에 병렬로 연결된 커패시 턴스에 영향을 받음

- 병렬 커패시턴스는 pn 접합간, 두 전극 사이 및 인접한 도전체 사이에서 발생 이를 기생 커패시턴스(stray capacitance)라 함

# □ 저역통과 RC회로망

▶ 위상:

$$\angle \left(v_o/v_i\right) = -tan^{-1}(\omega/\omega_A) = -tan^{-1}(f/f_A)$$

$\omega = 1/RC = \omega_A$ (차단주파수)일 때  $\angle \left(v_o/v_i\right) = -tan^{-1}(1) = -45^o$   $\rightarrow$  차단주파수에서  $v_o$ 의 위상은  $v_i$ 의 위상보다  $45^\circ$  뒤짐(lag) 입력주파수  $f = 0$ 일 때  $\angle v_o = 0^o$ ,  $f = \infty$ 일 때  $\angle v_o = -90^o$

## 1) 입력단 병렬커패시턴스 $C_A$ 의 영향

• 전압전달비:

$$\frac{v_{i}}{v_{s}} = \frac{-jX_{C_{A}} \parallel r_{i}}{r_{s} + (-jX_{C_{A}} \parallel r_{i})} = \frac{r_{i}/(1 + j\omega r_{i}C_{A})}{r_{s} + r_{i}/(1 + j\omega r_{i}C_{A})} = \frac{r_{i}}{r_{s} + j\omega r_{s}r_{i}C_{A} + r_{i}}$$

$$= \frac{r_{i}}{r_{i} + r_{s}} \cdot \frac{1}{1 + j\omega r_{s}r_{i}C_{A}/(r_{s} + r_{i})} = \frac{r_{i}}{r_{i} + r_{s}} \cdot \frac{1}{1 + \frac{j\omega}{\omega_{A}}}$$

$$|\frac{v_{i}}{v_{s}}| = \frac{r_{i}}{r_{s} + r_{i}} \cdot \frac{1}{\sqrt{1 + (\omega/\omega_{A})^{2}}} = \frac{r_{i}}{r_{s} + r_{i}} \cdot \frac{1}{\sqrt{1 + (f/f_{A})^{2}}}$$

- 차단주파수:  $\omega_A = \frac{1}{(r_i \parallel r_s) C_A}$  또는  $f_A = \frac{1}{2\pi (r_s \parallel r_i) C_A}$

- 위상:  $\angle (v_i/v_s) = -\tan^{-1}(\omega/\omega_A) = -\tan^{-1}(f/f_A)$

# 2) 출력단 병렬커패시턴스 $C_{\!B}$ 의 영향

• 차단주파수:  $f_B = \frac{1}{2\pi (r_o \parallel R_L) C_B}$

### 3) 입력단 및 출력단 병렬커패시턴스 모두의 영향

- 입력단 병렬커패시턴스  $C_A$ 에 의한 차단주파수:  $f_A = \frac{1}{2\pi (r_S \parallel r_i) C_A}$

- 출력단 병렬커패시턴스  $C_B$ 에 의한 차단주파수:  $f_B = \frac{1}{2\pi (r_o \parallel R_L) C_B}$

- 전체의 차단주파수  $f_H$ 과의 관계:  $f_H^{\ 4}=\left(f_A^{\ 2}+f_B^{\ 2}\right)f_H^{\ 2}-f_A^{\ 2}f_B^{\ 2}=0$  (부록 C)  $\to f_A\ll f_B$ 이면  $f_H\approx f_A$ ,  $f_A=f_B=f$ 이면  $f_H=0.645f$

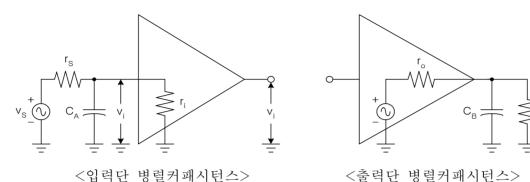

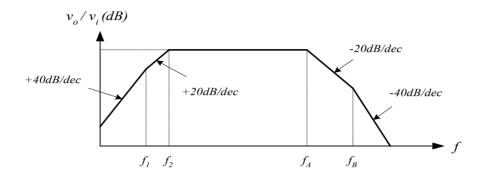

## ■ 전체 주파수특성

- 결합커패시터 $(C_1$  및  $C_2$ )와 병렬 커패시턴스 $(C_A$  및  $C_B$ ) 모두에 의한 주파수특성

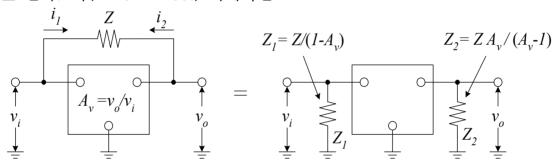

■ 밀러효과(Miller-Effect) 커패시턴스

$$\begin{aligned} \boldsymbol{\cdot} & \quad i_1 = \frac{v_i - v_o}{Z} = \frac{v_i \left(1 - A_v\right)}{Z} = \frac{v_i}{Z/(1 - A_v)} = \frac{v_i}{Z_1} \\ & \qquad \qquad \vdots \\ & \qquad \end{aligned}$$

•

$$i_2 = \frac{v_o - v_i}{Z} = \frac{v_o (1 - 1/A_v)}{Z} = \frac{v_o}{Z/(1 - 1/A_v)} = \frac{v_o}{Z_2}$$

$$\therefore \quad Z_2 = \frac{Z}{1 - 1/A_v} \quad \text{Fig. } Z_2 = \frac{Z \cdot A_v}{A_v - 1}$$

\*\* 커패시턴스  $C_c$ 가 입력단과 출력단 사이에 연결되었을 때  $Z{=}{-}jX_{C_c}=1/j\omega C_c$ . 이므로

$$C_1 = C_{c.}(1 - A_v)$$

및  $C_2 = (1 - 1/A_v)C_{c.}$

→ 예제 9-9)

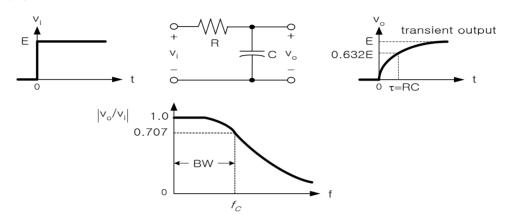

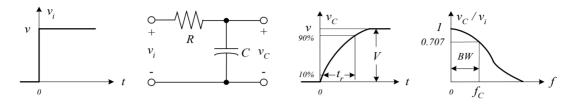

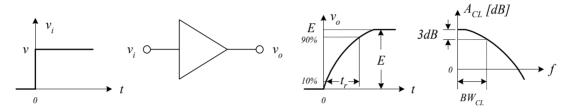

# ■ 과도응답(transient response)

- 과도응답: 시스템의 입력에 펄스 또는 급작스런 레벨변화가 인가될 때 출력되 는 파형

- 과도응답으로부터 주파수대역을 유추할 수 있음

- 1) 저역통과회로

- $BW = f_C = \frac{1}{2\pi\tau} = \frac{1}{2\pi RC}$

- 상승시간(rise time)  $t_r$  : 출력이 10%에서 90%까지의 시간

$$t_rpprox rac{0.35}{BW}$$

또는  $BWpprox rac{0.35}{t_r}$

2) 고역통과회로

• 새그(sag) : 피크전압에 대한 감소한 전압의 비

$$sag = \frac{\Delta V}{E_P} = 1 - e^{-\pi f_L/f}$$

(여기서,  $f$ 는 입력구형파의 주파수)

(예) sag가 0.18이고 f = 300Hz일 때  $f_L = 19Hz$

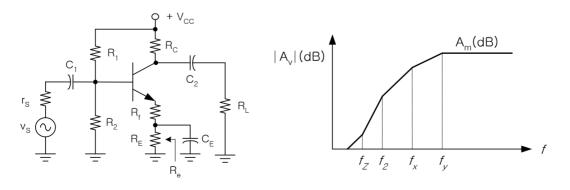

## ■ BJT증폭기의 주파수응답

## □ BJT증폭기의 저주파응답

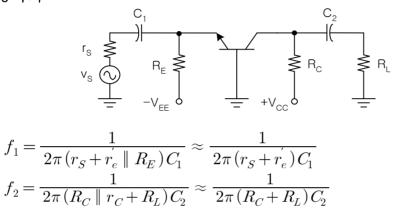

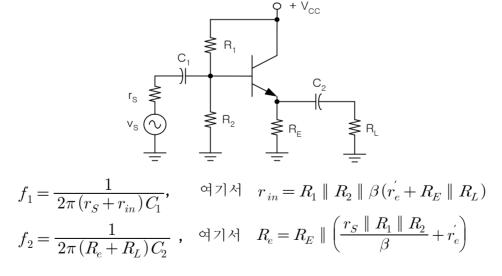

- 입력 결합 커패시턴스에 의한 차단주파수 :  $f_1 = \frac{1}{2\pi (r_i + r_S)C_1}$

- 출력 결합 커패시턴스에 의한 차단주파수 :  $f_2 = \frac{1}{2\pi \, (r_o + R_L) \, C_2}$

- 전체의 차단주파수  $f_L$ 과의 관계:  $f_L^{\ 4}=(f_1^{\ 2}+f_2^{\ 2})f_L^{\ 2}-f_1^{\ 2}f_2^{\ 2}=0$  (부록 C)

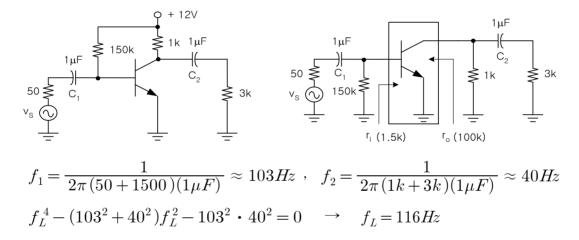

#### ▶ CE증폭기

예제 9-11)  $r_i=1.5k\Omega,\;r_o=100k\Omega$ 인 BJT의 저역 차단주파수는?

# lackbox 바이패스 커패시터 $C_{\!E}$ 를 가지는 ${ m CE}$ 증폭기

- 저역 차단주파수는 일반적으로  $C_1$  및  $C_E$ 에 주로 영향을 받음

•

$$C_1$$

에 의한 차단주파수 :  $f_b = \frac{1}{2\pi [r_S + R_B \parallel \beta (r_e + R_f)] C_1}$

•

$$C_E$$

에 의한 차단주파수 :  $f_e = rac{1}{2\pi R_e C_F}$

• 전체의 근사적 차단주파수 :  $f_L \approx f_b + f_e$

#### ▶ CB증폭기

예제 9-14)

$$r_S=100\Omega,\;R_C=1k\Omega,\;C_1=2.2\mu F\;,\;R_E=10k\Omega,\;R_L=15k\Omega,$$

$$C_2=1\mu F\; \rm 일\;\; \text{때} \quad f_1=579Hz\;\; \rm 및 \quad f_2=9.9Hz$$

$$\to \quad f_1\gg f_2 \quad \text{이므로} \quad f_L=f_1=579Hz$$

#### ▶ CC증폭기

예제 9-14)

$$r_S=100\Omega,\; R_E=1k\Omega,\; C_1=2\mu F,\; R_1=33k\Omega\,,\; R_L=50\Omega,$$

$$C_2=10\mu F,\;\; R_2=10k\Omega\, \rm 일\;\; 때 \quad f_1=20.8 Hz\;\; 및 \quad f_2=212 Hz$$

$$\to \quad f_1 < f_2 \quad \mbox{이므로} \quad f_L \approx f_2=212 Hz$$

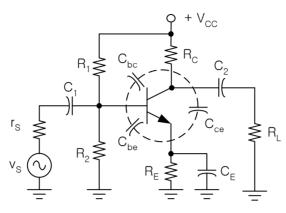

## □ BJT증폭기의 고주파응답

#### ▶ CE증폭기

$lackbox{} C_{bc}$ 를 밀러효과를 이용하여 좌우로 분리하면

$$C_A = C_{be} + C_{bc}(1 - A_v)$$

및  $C_B = C_{ce} + C_{bc}(1 - 1/A_v)$ 이 됨

•

$$C_A$$

에 의한 차단주파수:  $f_A = \frac{1}{2\pi(r_s \parallel r_i)C_A}$  , 여기서  $r_i = R_1 \parallel R_2 \parallel (\beta r_e{}')$

•

$$C_B$$

에 의한 차단주파수:  $f_B = \frac{1}{2\pi(r_{out} \parallel R_L)C_B}$  , 여기서  $r_{out} = r_o \parallel R_C$

• 전체 차단주파수:

$$f_H pprox \dfrac{1}{\dfrac{1}{f_A} + \dfrac{1}{f_R}}$$

예제 9-16)  $C_{be}=40pF,\ C_{bc}=1.5pF,\ C_{ce}=1pF,\ A_v=-166.67$ 일 때

$$\begin{split} C_A &= C_{be} + C_{bc}(1 - A_v) = 291.5pF & \to & f_A = 2.95MHz \\ C_B &= C_{ce} + C_{bc}(1 - 1/A_v) = 2.5pF & \to & f_B = 11.1MHz \end{split}$$

$$\therefore f_H \approx \frac{1}{\frac{1}{f_A} + \frac{1}{f_B}} = 2.33 MHz$$

※ 전체 차단주파수에 큰 영향을 주는 것은  $C_{bc}$ 의 입력단 밀러커패시턴스  $C_{M}$ 임.  $C_{M}=C_{bc}(1-A_{v})$ . 증폭도  $A_{v}$ 가 클수록 밀러커패시턴스가 커지므로 차단주파수가 낮아져서 전체의 주파수대역을 적게 만듦

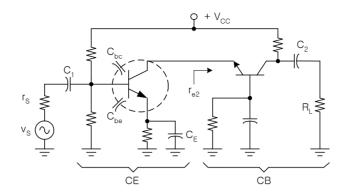

#### ▶ Cascode 증폭기 (CE-CB)

- 단일 CE증폭기의 주파수대역을 넓히기 위해 CE의 부하로 CB를 사용

- 전체차단주파수에 영향을 주는 것은 부하저항은 CB의 입력저항  $r_{e2}$ 이고 이는 적은 값이므로 CE의 증폭도  $A_{n1} \approx -1$ 임

- 증폭도가 작으므로 밀러커패시턴스도 작아져서 주파수특성이 우수함

## ■ FET증폭기의 주파수응답

- BJT 증폭기와 표기만 다를 뿐 서로 동일함

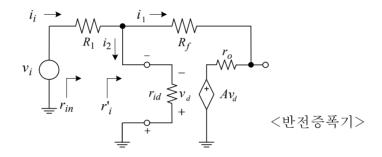

## □ FET증폭기의 저주파응답

- $C_1$ 에 의한 차단주파수 :  $f_1=\frac{1}{2\pi(r_{in}+r_s)C_1}$  여기서  $r_{in}\approx R_1\parallel R_2$

- $C_2$ 에 의한 차단주파수 :  $f_2 = \frac{1}{2\pi(r_{out} + R_L)C_2}$  여기서  $r_{out} \approx r_d \parallel R_D$

- $C_S$ 에 의한 차단주파수 :  $f_S = \frac{1}{2\pi [R_S \parallel (1/g_m)] C_S}$

- 전체 차단주파수  $f_L$ 은 3개 중 가장 큰 주파수로 근사

# ㅁ FET증폭기의 고주파응답

- 입력단 커페시턴스에 의한 차단주파수 :  $f_A{}' = \frac{1}{2\pi(r_s \parallel r_{in})C_A{}'}$  여기서  $C_A{}' = C_{gs} + C_M = C_{gs} + C_{gd}(1-A_v), \; r_{in} = r_i \approx R_1 \parallel R_2$

- 입력단 커패시턴스에 의한 차단주파수 :  $f_B^{\ \prime} = \frac{1}{2\pi(r_{out} \parallel R_L)C_B^{\ \prime}}$  여기서  $C_B^{\ \prime} = C_{ds} + C_{gd}(1-1/A_v), \quad r_{out} \approx r_d \parallel R_D$

- 전체 차단주파수  $f_H$ 는 2개 중 가장 적은 주파수로 근사

# Chap. 10 OP Amp Theory and Performance

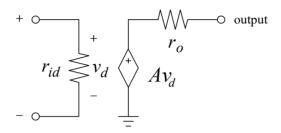

#### ■ OP Amp의 모델링

- 이상적인 OP amp(이득: ∞, 입력임피던스: ∞, 출력임피던스: 0) → 8장

- 실질적이고 비이상적인 OP amp의 회로모델

• 741 OP amp의 경우:  $A\approx 200,000,\;r_{id}\approx 2M\Omega,\;\;r_o\approx 75\Omega$

#### ■ OP Amp의 모델링

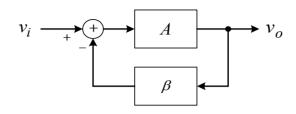

- OP amp의 폐루프이득(closed-loop gain)  $v_o/v_i$ 는 외부 저항의 피드백연결에 의해 결정됨

#### ◎ 비반전증폭기의 피드백(feedback)

-  $r_{id}\gg R_{\rm l},R_{\rm f}$  및  $r_o\ll R_{\rm l},R_{\rm f}$  이라 가정하면

$$v_i^- = \left(\frac{R_1}{R_1 + R_f}\right) v_o$$

- 궤환률(feedback ratio)  $\beta$ 를  $\beta=R_{\rm l}/(R_{\rm l}+R_{\rm f})$ 라 두면  $v_i^-=\beta v_o$

- 출력전압  $v_o = A(v_i \beta v_o) = Av_i A\beta v_o \implies (1+A\beta) v_o = Av_i$

- 폐루프이득:

$$A_{\mathit{CL}} = \frac{v_o}{v_i} = \frac{A}{1 + A\beta}$$

$$A=\infty$$

이면  $A_{CL}=rac{1}{eta}=rac{R_{\mathrm{l}}+R_{\mathrm{f}}}{R_{\mathrm{l}}}=1+rac{R_{\mathrm{f}}}{R_{\mathrm{l}}}$  (이상적 증폭기의 결과)

예제 10-1)  $R_1=10k\Omega,\;R_f=90k\Omega$ 인 비반전증폭기의 폐루프이득?

sol)

$$\beta = R_1/(R_1 + R_f) = 10k\Omega/(10k\Omega + 90k\Omega) = 0.1$$

(a)

$$A = \infty$$

일 때:  $A_{CL} = 1/\beta = 1/0.1 = 10$

(b)

$$A = 10^6$$

일 때:  $A_{CL} = \frac{A}{1 + A\beta} = \frac{10^6}{1 + 10^6(0.1)} = 9.99990$

(c)

$$A=10^3$$

일 때:  $A_{CL}=\frac{A}{1+A\beta}=\frac{10^3}{1+10^3(0.1)}=9.90099$  (1% 차이)

\_\_\_\_\_

- 실제적 폐루프이득:  $A_{CL}=\frac{1/\beta}{1+1/A\beta}=\frac{1+R_f/R_1}{1+(R_1+R_f)/AR_1}$ 이상적 폐루프이득을  $\hat{A}_{CL}=1+R_f/R_1$ 이라 두면

$$A_{CL} = \frac{\hat{A}_{CL}}{1 + 1/A\beta} = \frac{\hat{A}_{CL}}{1 + \hat{A}_{CL}/A}$$

예제 10-2) 개루프이득(open loop gain) A=10,000인 비반전증폭기의 실제적 폐루프이득?

(a)

$$R_f = 24k\Omega$$

,  $R_1 = 1k\Omega$  일 때 $(\beta = 1/25)$  :  $\hat{A}_{CL} = 25$ ,  $A_{CL} = 24.94$  (99.76%)

(b)

$$R_{\!f}=49k\Omega,~R_{\!1}=1k\Omega$$

일 때 $(\beta=1/50)$  :  $\hat{A}_{\it CL}=50$  ,  $A_{\it CL}=49.75$  (99.50%)

(c)

$$R_f = 99k\Omega$$

,  $R_1 = 1k\Omega$ 일 때 $(\beta = 1/100)$ :  $\hat{A}_{CL} = 100$ ,  $A_{CL} = 99.01$  (99.01%)

st A 및 eta가 클수록 폐루프이득이 이상적인 값인 1/eta에 접근

#### □ 입력저항(음궤환을 통한 폐루프 입력저항)

- 입력전류:  $i_i = \frac{v_i \beta v_o}{r_{id}} = \frac{v_i \beta A i_i \, r_{id}}{r_{id}} \qquad \rightarrow \qquad i_i \, r_{id} (1 + A \beta) = v_i$

- 페루프 입력저항:  $\dfrac{v_i}{i_i} = r_i = r_{id}(1+Aeta)$

- ※ 음궤환(negative feedback) 폐루프 입력저항은 개루프 입력저항  $r_{id}$ 의 1+Aeta 배로 증가  $\rightarrow$  음궤환으로 인해 입력저항이 증가하므로 증폭기의 성능 개선

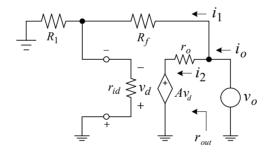

# □ 출력저항(음궤환을 통한 폐루프 출력저항)

• KCL을 사용하면  $i_o = i_1 + i_2$

여기서,

$$i_1 = \frac{v_o}{R_f + r_{id} \parallel R_1}$$

및  $i_2 = \frac{v_o - Av_d}{r_o}$

- $R_1 \ll r_{id}$ 라 가정하고,  $v_d = -\beta v_o$ 이므로  $i_o = \frac{v_o}{R_f + R_1} + \frac{v_o(1 + A\beta)}{r_o}$

- 첫 번째 항이 두 번째 항에 비해 훨씬 적으므로 무시하여 출력저항을 구하면

$$\frac{v_o}{i_o} = r_{out} = \frac{r_o}{1 + A\beta}$$

- lpha 음궤환 폐루프 출력저항은 개루프 출력저항  $r_o$ 의 1/(1+Aeta)배로 감소

- → 음궤환으로 인해 출력저항이 감소하므로 증폭기의 성능 개선

## ◎ 반전증폭기의 피드백(feedback)

•

$$\frac{v_i - v_i^-}{R_1} = \frac{v_i^- - v_o}{R_f}$$

및  $v_i^- = - v_o/A$ 이므로  $\frac{v_i}{R_1} + \frac{v_o}{AR_1} = \frac{-v_o}{AR_f} - \frac{v_o}{R_f}$

• 증폭도:

$$\frac{v_o}{v_i} = \frac{-R_f/R_1}{1+(R_1+R_f)/AR_1}$$

(  $A = \infty$ 일 때  $\hat{A}_{CL} = -\frac{R_f}{R_1}$  )

• 궤환율  $eta = R_1/(R_1 + R_f)$ 이므로 (반전 및 비반전 증폭기의 궤환율은 동일)

$$A_{CL} = \frac{v_o}{v_i} = \frac{-R_f/R_1}{1 + 1/A\beta} = \frac{\hat{A}_{CL}}{1 + 1/A\beta}$$

□ 반전 입력저항(음궤환을 통한 폐루프 입력저항)

• KCL을 사용하면

$$i_i = \frac{v_i^-}{r_{id}} + \frac{v_i^- - A v_d}{R_f + r_o}$$

•

$$v_d = -v_i^-$$

를 대입하면  $i_i = \frac{v_i^-}{r_{id}} + \frac{(1+A)v_i^-}{R_f + r_o} pprox \frac{Av_i^-}{R_f}

ightarrow \frac{v_i^-}{i_i} = r_i^{'} pprox \frac{R_f}{A}$

• 입력저항:

$$r_{in} \approx R_1 + \frac{R_f}{A} \rightarrow A = \infty$$

일 때  $r_{in} = R_1$ ,  $r_i^{'} = 0$  (virtual ground)

#### □ 반전 **출력저항**(음궤환을 통한 폐루프 출력저항)

• 출력저항:

$$r_{out} = \frac{r_o}{1+A\beta} \approx \frac{r_o}{A\beta}$$

(비반전과 동일함)

예제 10-3)  $R_1=1.5k\Omega,\;R_f=150k\Omega,\;A=2500$  및  $r_o=100\Omega$ 인 반전증폭기

① 루프이득(loop gain) :

$$A\beta$$

여기서  $\beta=R_1/(R_1+R_f)$

② 폐루프이득:

$$A_{C\!L} = \frac{v_o}{v_i} = \frac{-R_f/R_1}{1+1/A\beta} = -96.12$$

③

$$v_i$$

에서 본 입력저항:  $r_{in}=R_1+\frac{R_f}{A}$  =  $1560$   $\Omega$

④ 폐루프 출력저항:

$$r_{out} = \frac{r_o}{1 + A\beta} = 3.88\Omega$$

- 피드백이론에 의한 실제 페루프이득  $A_{C\!L}$ 과 이상적인 페루프이득  $\hat{A}_{C\!L}$ 과의 관계

$$A_{\mathit{CL}} = actual \, \frac{v_o}{v_i} = \frac{\hat{A}_{\mathit{CL}}}{1 + 1/A\beta}$$

- 이 관계는 비반전 및 반전증폭기 모두에 적용

$$A_{CL} = \frac{v_o}{v_i} = \frac{\hat{A}_{CL}}{1 + 1/A\beta} = \frac{1 + R_f/R_1}{1 + 1/A\beta} \qquad \qquad (비반전증폭기)$$

$$A_{CL} = \frac{v_o}{v_i} = \frac{\hat{A}_{CL}}{1 + 1/A\beta} = \frac{-R_f/R_1}{1 + 1/A\beta} \qquad \qquad (반전증폭기)$$

ightarrow 루프이득Aeta 값이 클수록  $A_{C\!L}pprox \hat{A}_{C\!L}$

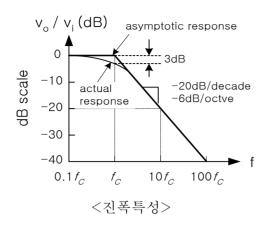

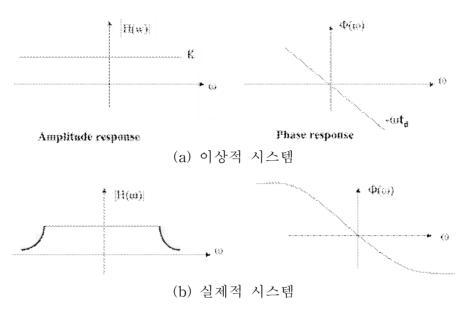

#### ■ 주파수응답(frequency response)

- 신호주파수가 개방루프와 폐루프이득에 미치는 효과에 대해 공부

- 입력주파수가 연산증폭기의 폐루프 대역폭이 궤환률 β의 연관성을 공부

- 피드백을 통해 증폭기의 주파수대역 개선을 공부

#### ㅁ 안전성(stability)

- 안정성: 증폭기가 발진(oscillation)이 되지 않고 정상적인 증폭동작특성을 가지 는 것

- 발진은 높은 이득, 광대역 증폭기에서 리액턴스 요소를 통해 발생하는 정궤환 (positive feedback) 때문에 발생

- 대부분의 연산증폭기는 매우 큰 이득을 가지고 있으므로 발산하지 않게 하기위 해 내부 보상회로를 사용하여 개방루프이득의 주파수대역을 줄임

- → 단일 RC회로망의 단일극점(single-pole)주파수응답을 가지는 것으로 취급

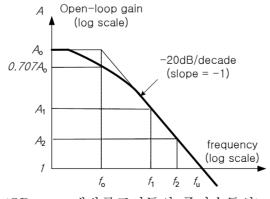

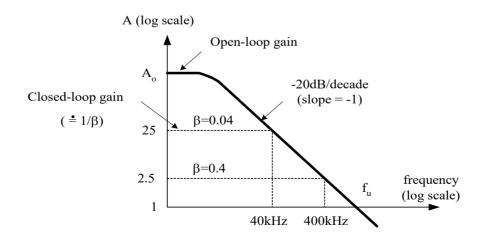

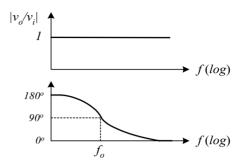

#### ㅁ 이득-대역폭 곱(The Gain-Bandwidth Product)

<OP amp 개방루프이득의 주파수특성>

- 단일극점 주파수응답을 가지고 있는 증폭기의 개방루프이득에 대한 전형적인 로그-로그좌표의 주파수응답 특성

- 차단주파수(cutoff frequency)  $f_0$ : 저주파 또는 dc이득  $A_0$ 의 0.707배인 주파수

- 단일극점응답의 기울기는 로그-로그좌표에서 -1

- 이득-대역폭곱(GBP):  $A_1f_1=A_2f_2=A_0f_0=1f_u=GBP$   $\rightarrow$   $f_u=A_0f_0$  여기서  $f_u$  = 단위이득주파수, 이득이 1일 때의 주파수

- 폐루프대역폭 $(BW_{CT})$ 과 이득-대역폭곱 사이의 근사적 관계(부록 $\mathbb C$  참조):

$$BW_{CL} = f_{\nu}\beta = A_0 f_0 \beta = \beta GBP$$

( $\beta$ 는 궤환률)

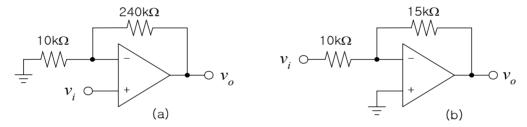

예제 10-5) 증폭기들의 개방루프 이득-대역폭곱은  $1\times 10^6 Hz$ 이다. 다음 그림과 같은 폐루프로 구성되었을 때의 차단주파수들을 각각 구하여라.

- sol) (a)  $\beta = R_1/(R_1 + R_f) = (10k\Omega)/[(10k\Omega) + (240k\Omega)] = 0.04$   $BW_{CL} = \beta \ GBP = (0.04)(10^6) = 40kHz$  폐루프 차단주파수는 폐루프대역폭 40kHz와 같음

- (b)  $\beta = R_1/(R_1 + R_f) = (10k\Omega)/[(10k\Omega) + (15k\Omega)] = 0.4$  따라서  $BW_{CL} = (0.4)10^6 = 400kHz$

- % 계환률  $\beta$ 가 클수록(페루프이득이 적을수록) 페루프대역폭이 증가

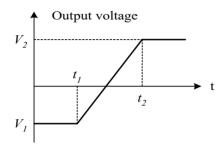

## ■ 슬루율(slew rate) 및 상승시간(rise time)

▶ 슬루율: 증폭기에 계단(step) 또는 펄스형태의 신호가 인가될 때 출력전압이 변할 수 있는 최대 가능한 초당 전압의 비율

변화율

$$= rac{V_2 - V_1}{t_2 - t_1} = rac{arDelta\,V}{arDelta\,t}$$

[  $V/s$  ]

- 증폭기의 슬루율은 출력이 변화할 수 있는 최대 비율임

- 예) 슬루율이  $10^6 V/s$ 인 증폭기

- (a) 0.1 μs 내에 -5V에서 +5V로 변하는 입력신호로 이득이 1인 증폭기 출력의 변화율 ΔV/Δt = (10V)/(10<sup>-7</sup>s) = 10<sup>8</sup>V/s

→ 슬루율 10<sup>6</sup> V/s을 초과하므로 출력파형이 왜곡됨

- (b)  $1\,\mu s$ 내에  $0{\rm V}$ 에서  $1{\rm V}$ 로 변하는 입력으로 10배의 이득을 가진 증폭기 출력의 변화율이  $\Delta {\rm V}/\Delta t = 10/10^{-6} = 10^7 {\rm V/s} \rightarrow$  슬루율 초과로 출력이 왜곡

- 증폭기의 출력이 사인파전압  $v_0(t)=V_P\sin wt$ 일 때 t에 대해 미분을 하여 구한 최대변화율: 변화율(최대) =  $V_Pw$  [volts/second]

- 증폭기의 슬루율을 S라 하면  $V_p w \leq S$  또는  $2\pi f V_P \leq S$

- 증폭기의 출력에서 슬루율의 한계를 허용하는 최대주파수는  $f_s(\max) = \frac{S}{2\pi V_P} \qquad \text{또는} \qquad w_s(\max) = \frac{S}{V_P}$

- $V_{I}$

- 최소의 슬루율을 결정하는데 사용되는 조건

$$S \ge 2\pi f_{\max} V_P(\max)$$

- 연산증폭기회로가 주파수 f의 신호성분을 왜곡하지 않기 위한 두 조건

$$f \leq BW_{CL}$$

및  $f \leq S/2\pi V_P$

- ▶ 상승시간: 계단파 입력의 출력이 최종값의 10%에서 90%까지 걸리는 시간

- 단일극점 RC회로에서 상승시간은  $t_r = 0.35/BW$

- $v_c(t) = V(1 e^{-t/RC}) = V(1 e^{-2\pi f_c t})$ , 여기서  $f_c = 1/2\pi RC$

- 단일극점 궤환증폭기에서 상승시간은  $t_r = 0.35/BW_{CL}$

•  $v_o(t)=E(1-e^{-t/RC})=E(1-e^{-2\pi f_c t})$  대역-이득곱:  $GBP=A_{CL}\cdot BW_{CL}$

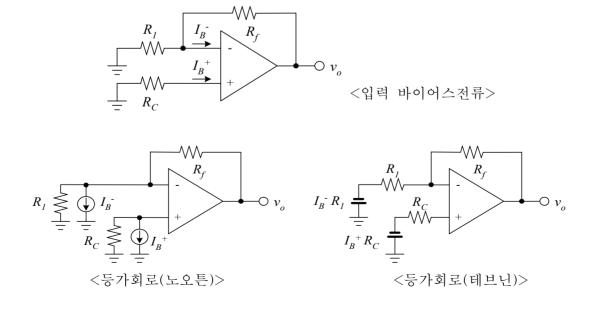

## ■ 오프셋(offset) 전류 및 전압

#### □ 입력 바이어스전류

- 입력신호들이 접지되었을 때 연산증폭기의 +와 -단자에 흐르는 전류:  $ec{arGamma}$ 와  $ec{arGamma}$

- 입력 바이어스 전류:  $I_B = (I_B^+ + I_B^-)/2$

#### ㅁ 입력 오프셋(offset)전류

두 입력단의 바이어스전류의 절대오차:  $I_{io} = I_B^+ - I_B^-$

#### □ 바이어스전류에 의한 출력 오프셋전압

•  $I_R^- R_1$ 에 기인하는 출력(+ 단자에 연결된 입력원은 접지):

$$V_{o1} = -I_B^- R_1 (\frac{-R_f}{R_1}) = I_B^- R_f$$

•  $I_B^{+}R_C$ 에 기인하는 출력(- 단자에 연결된 입력원은 접지) :

$$V_{02} = -I_B^+ R_C \left(1 + \frac{R_f}{R_1}\right)$$

• 총 출력오프셋전압  $V_{OS}(I_B)$  :

$$\begin{split} V_{OS}(I_B) &= I_B^- R_f - (1 + \frac{R_f}{R_1}) I_B^+ R_C \qquad (*) \\ V_{OS}(I_B) &= I_{BB} [R_f - (1 + \frac{R_f}{R_1}) R_C] \qquad \longleftarrow \quad I_B^+ = I_B^- = I_{BB} 일 \ \, & \text{때} \end{split}$$

- 중괄호 내의 식이 영이라면 오프셋전압은 영이 됨.

$$R_f - (1 + \frac{R_f}{R_1})R_C = 0$$

\*\* 보상저항  $R_C$  :  $R_C = \frac{R_f R_1}{R_f + R_1} = R_f \parallel R_1$  (반전 및 비반전 모두 적용)

- 식 (\*)에  $R_C=R_1\parallel R_f$ 를 대입하면 (여기에서는  $I_B^+=I_B^-$  가정이 없음)

$$V_{OS}(I_B) = I_B^- R_f - I_B^+ \left(\frac{R_1 R_f}{R_1 + R_f}\right) \left(\frac{R_1 + R_f}{R_1}\right)$$

$$= (I_B^- - I_B^+) R_f$$

- 부호와 관계없는 절대치 표현:

$$V_{OS}\left(I_{B}

ight) = I_{io}R_{f} \qquad \left(R_{C} = R_{1} \parallel R_{f} \, \stackrel{\mathrm{cl}}{=} \, \, \, \mathrm{때}

ight)$$

여기서,  $I_{io}=I_B^+-I_B^-$  : 입력오프셋전류

예제 10-13) 입력바이어스전류 $(I_B)$ 가 80nA, 입력오프셋전류 $(I_{io})$ 가 최대 10nA

- (a) 보상저항  $R_C$ 의 최적값 :  $R_C=R_1 \parallel R_f=(10k\Omega) \parallel (100k\Omega)=9.09k\Omega$

- (b)  $R_C$ 가 최적값일 때 바이어스 오프셋전류로 인한 최대 출력오프셋전압 :  $V_{OS}(I_B) \; = \; I_{io}R_f \; = \; (10 \; \times \; 10^{-9})(100 \; \times \; 10^3) \; = \; 1 \mathrm{mV}$

- (c)  $I_{io}=10nA,~I_B^+~>I_B^-$ 이라고 가정하고,  $R_C=0$ 일 때 출력오프셋전압의 크기 :  $I_{io}=~I_B^+-I_B^-~,~I_B=\left(I_B^+-I_B^-\right)/2$ 로부터  $I_B^+=85$ nA 및  $I_B^-=75$ nA  $R_C=0$ 일 때  $V_{OS}(I_B)=I_B^-R_f~\to~V_{OS}(I_B)=(75\times10^{-9})(100\times10^3)=7.5$ mV ※ 보상저항이 없으면 오프셋전압은 크게 증가한다는 것을 알 수 있음

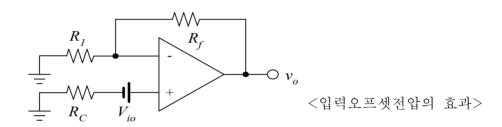

## □ 입력 오프셋전압

- 입력오프셋전압( $V_{io}$ ): 입력차동단의 BJT들의 불완전한 정합 때문에 내부적으로 생성되는 전위차 (출력오프셋전압을 발생시킴)

- 입력오프셋전압에 의한 출력오프셋전압 :  $V_{OS}(V_{io}) = V_{io}(1 + \frac{R_f}{R_1})$

- 출력오프셋전압과 궤환율 eta와의 관계 :  $V_{OS}(V_{io}) = V_{io}/eta$

#### □ 총 출력오프셋전압

- 총 출력오프셋전압은 입력바이어스전압 및 입력오프셋전압에 의한 오프셋전압 의 합:

$$\mid V_{OS} \mid = \mid V_{OS}(I_B) \mid + \mid V_{OS}(V_{io}) \mid$$

(최악의 경우)

- $R_{C}=R_{1}\parallel R_{f}$  일 때  $\mid V_{OS}\mid =I_{io}R_{f}+\mid V_{OS}\left(V_{io}

ight)\mid$

- → 예제 10-15), 10-16)

# Chap. 11 Advanced operational amplifier applications

## ■ Electronic integration (전자적분)

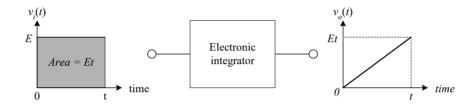

- 전자적분기 : 임의 시간 t의 순간 출력  $v_o(t)$ 이 그 시간까지의 입력파형  $v_i(t)$ 의 총 면적과 같이 되는 장치

$$v_o(t) = \int_0^t v_i(t) dt$$

예) 입력의 E가 5V dc전압이면, 출력은 t=1초일 때 5V, t=2초일 때 10V, t=3초일 때 15V가 되므로 램프전압  $v_o(t)=Et$ 임

▶ 연산증폭기를 사용한 전자적분기

$$v_{i} \circ \bigvee_{i_{l}} v_{o}(t)$$

$$R_{C} = R_{l} \underbrace{\sum_{i_{l}} v_{o}(t)} v_{o}(t) = -\frac{1}{R_{1}C} \int_{0}^{t} v_{i} dt$$

- 입력단자에 인가되는 전류는 0이기 때문에,  $i_1+i_C=0$

$$\begin{split} i_1 &= \frac{v_i}{R_1} \,, \quad i_C = C \frac{dv_o}{dt} \quad (\because \quad v^- = 0) \\ &\frac{v_1}{R_1} + C \frac{dv_o}{dt} = 0 \qquad \text{혹은} \qquad \frac{dv_o}{dt} = \frac{-1}{R_1 C} v_i \\ &t \text{에 관해 양변을 적분하면,} \quad v_o = \frac{-1}{R_1 C} \int_0^t v_i dt \end{split}$$

예) 반전적분의 입력이  $v_i = Asin\omega t$ 일 때의 출력은  $v_o = \frac{-1}{R_1C}\int (Asin\omega t)dt = \frac{-A}{\omega R_1C}\left(-\cos\omega t\right) = \frac{A}{\omega R_1C}\left(\cos\omega t\right)$

→ 예제 11-1)

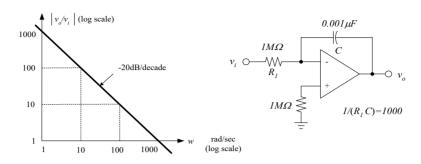

#### ▶ 적분기의 주파수 특성

<R<sub>1</sub>C=0.001일 경우의 보드선도>

- 이득크기 (입력 피크값에 대한 출력 피크값의 비)

$$\left| \begin{array}{c} \frac{v_o}{v_i} \end{array} \right| = \frac{A/\omega R_1 C}{A} = \frac{1}{\omega R_1 C}$$

- 이득이 주파수 ω에 반비례 (기울기: -20dB/decade 또는 -6 dB/octave)

- 단위이득의 개방루프주파수  $f_{y}$ 는 연산증폭기의 이득-대역폭곱(GBP)과 같음

- 적분기의 단위이득 각주파수는  $1/R_1C$ 임 (주파수는  $1/2\pi R_1C$ 임)

- Op-amp 적분기의 동작 영역: 1/(2πR<sub>1</sub>C) < GBP

### ▶ 적분기의 응용

- 고주파수의 잡음을 줄이는 데 유용

- 미분방정식의 해를 실시간으로 구하기 위한 아날로그 컴퓨터에 사용

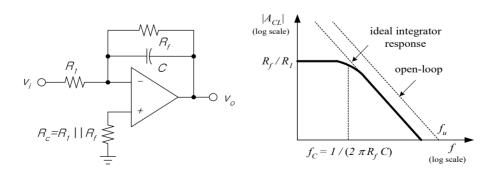

#### ㅁ 실제적 적분기

- 고성능 정밀적분기에 사용하는 Op-amp는 매우 작은 offset전압을 가져야 함 일부의 입력 offset전압은 dc신호입력처럼 적분되어 증폭기를 포화시킴

- 이 문제를 해결하기 위한 실질적인 적분기

- 저주파수일 때 :  $\mathit{C}$ 는 개방이 되어 반전증폭기로 동작 (폐루프이득 :  $-\mathit{R_f}/\mathit{R_1}$ )

- 고주파수일 때: C의 임피던스가  $R_f$ 보다 훨씬 더 작아져서 적분기로 동작  $\rightarrow$  이 적분기를 ac 적분기라고 함

- 적분기 동작 범위:  $X_{C}=R_{f}$ 의 주파수보다 더 큰 주파수에서 정상적 동작

$$X_C \ll R_f$$

,  $\frac{1}{2\pi fC} \ll R_f$  또는  $f \gg \frac{1}{2\pi R_f C}$

- 실제적인 적분기의 절점주파수(break frequency):

$$f_C = \frac{1}{2\pi R_f C}$$

- → 예제 11-2)

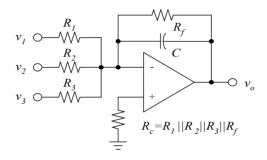

- ▶ 3-입력 적분기

- 출력:

$$\begin{split} v_o = & -\int \left(\frac{1}{R_1 C} v_1 + \frac{1}{R_2 C} v_2 + \frac{1}{R_3 C} v_3\right) \! dt \\ v_o = & -\frac{1}{R_1 C} \int v_1 dt - \frac{1}{R_2 C} \int v_2 dt - \frac{1}{R_3 C} \int v_3 dt \end{split}$$

만약

$$R_1=R_2=R_3$$

이면

$$v_o=-\frac{1}{R_1C}\int \left(v_1+v_2+v_3\right)dt$$

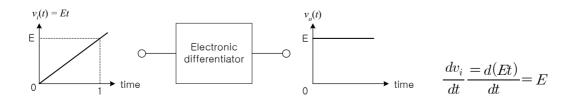

#### ■ Electronic differentiation (전자미분)

- 전자미분기: 임의 시간의 출력값은 그 시점의 입력 변화율과 같은 장치예)

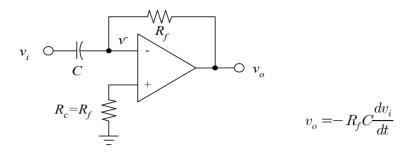

▶ Op amp를 사용한 전자미분기

- 단자 내에 흐르는 전류는 영이므로,  $i_c+i_f=0$

$$v^-=0$$

이므로,  $v_c=v_i$ 이고  $i_c=C\frac{dv_i}{dt}$

$$i_f=\frac{v_o}{R_f}$$

이므로  $C\frac{dv_i}{dt}+\frac{v_o}{R_f}=0$  또는  $v_o=-R_fC\frac{dv_i}{dt}$

- 미분기의 입력이  $v_i = A sin \omega t$ 일 때의 출력:

$$v_o = \frac{d(Asin\omega t)}{dt} = A\omega cos\omega t$$

$\rightarrow$  진폭은 주파수에 비례

- Op amp를 사용한 전자미분기의 입력이  $v_i = A sin \omega t$ 일 때의 출력 :

$$v_{o} = -R_{f}C\frac{d\left(Asin\omega t\right)}{dt} = -A\omega R_{f}Ccos\left(\omega t\right) = A\omega R_{f}Csin\left(\omega t - 90^{o}\right)$$

- → 출력은 주파수에 관계없이, 입력을 90° 지연시킴

- 미분기의 이득:

$$\left| \frac{v_o}{v_i} \right| = \frac{A\omega R_f C}{A} = \omega R_f C$$

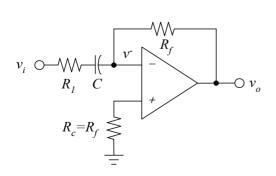

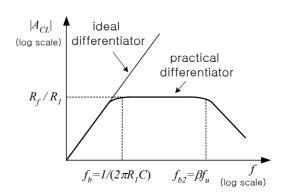

#### ㅁ 실제적 미분기

- 미분기가 가지는 근본적인 문제점: 출력은 입력의 주파수에 비례하여 증폭되므로 고주파의 잡음도 증폭됨

- 실제적 미분기

• R<sub>1</sub>-C 결합의 임피던스:

$$Z_i = R_1 - j/\omega C \qquad \mbox{"!} \qquad \left| Z_i \right| = \sqrt{R_1^2 + \left(1/\omega \, C\right)^2} \label{eq:Zi}$$

- 저주파수일 때 :  $Z_i$ 가 용량성 리액턴스 성분이 우세하므로 미분기로 동작

- 고주파수일 때 :  $1/\omega C$ 는 무시되므로  $Z_i$ 는 저항  $R_1$ 과 같아져 반전증폭기로 동작 (이득은  $-R_{\rm f}/R_{\rm l}$ )

- 미분이 되지 않기 시작하는 경계주파수인 절점주파수  $f_b$ 는 C의 용량성 리액턴 스와  $R_{\scriptscriptstyle \parallel}$ 의 저항성이 같아질 때의 주파수임

$$\frac{1}{2\pi f_b C} = R_1 \qquad \to \qquad f_b = \frac{1}{2\pi R_1 C}$$

- 절점주파수  $f_b$ 는 정확히 미분이 되는데 필요한 가장 높은 주파수  $f_h$ 보다 충분 히 높도록 설정

$$f_b \gg f_b$$

- 폐루프 대역폭 또는 증폭기의 상측 차단주파수:

$$f_2 = \beta f_u$$

(여기서  $\beta = R_1/(R_1 + R_f)$ )

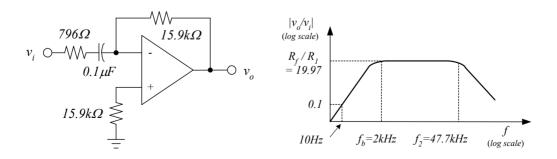

예제 11-3)

- 1. 최대주파수가 200Hz인 신호를 미분할 실제적인 미분기를 설계하라. 10Hz에서의 이득은 0.1이다.

- 2. 만약 이 설계에 사용된 연산증폭기가 1MHz에서 단위이득주파수를 가진다면, 이 미분기의 상측 차단주파수는 얼마인가?

#### 풀이

$1.~f_h=200Hz$  보다 높은 절점주파수  $f_b$ 를 만들기 위해  $R_1$  및 C를 선택해야 함.  $f_b=10f_h=2kHz~(f_b$ 의 10배)로 선택하고  $C=0.1\mu F$  라고 하면,

$$f_b = 2 \times 10^3 = \frac{1}{2\pi R_1 C} \ , \quad \ R_1 = \frac{1}{2\pi (2 \times 10^3)(10^{-7})} = 796 \Omega$$

을 얻는다. 10Hz에서 이득이 0.1이므로

$$\left| \frac{v_o}{v_i} \right| = 0.1 = \omega R_f C = (2\pi \times 10) R_f (10^{-7}) \rightarrow R_f = \frac{0.1}{2\pi \times 10 \times 10^{-7}} = 15.9 k\Omega$$

을 구할 수 있다.

$$2.~\beta = \frac{R_1}{R_1 + R_f} = \frac{796}{796 + 15.9k} = 0.0477$$

이므로  $f_2 = \beta f_u = 0.0477 imes 1 MHz = 47.7kHz$

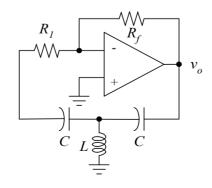

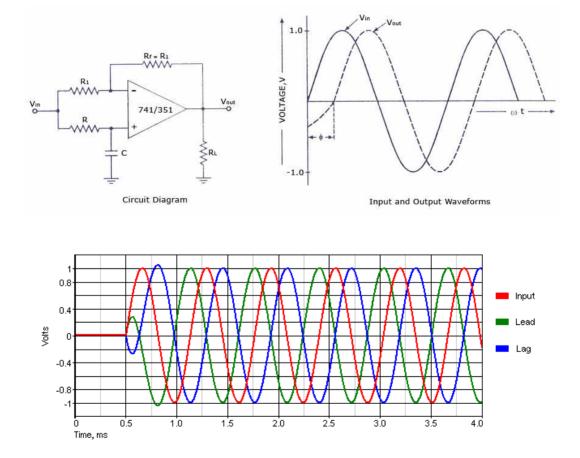

## ■ 위상이동(phase-shift)회로

- 적분기와 미분기회로들은 그들의 정상적인 동작영역 내에서 주파수에 관계없이 일정한 위상이동이 발생

- 일정지연필터(constant-delay filter) 또는 전역통과필터(all-pass filter): 주파수에는 의존하지만 일정한 이득을 유지하는 위상이동을 발생하는 회로

- 일정지연: 주파수가 변할 때, 입력과 출력 사이의 시간차가 동작하는 주파수의 범위에서 일정히 유지

- 전역통과(all-pass): 동작범위 안의 모든 주파수에서 일정한 이득(보통 1)을 유지

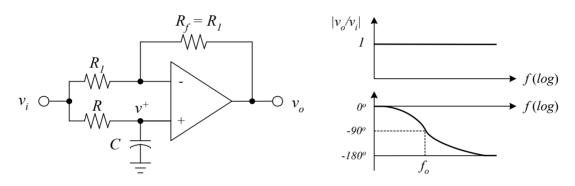

#### ㅁ지상(phase-lag)회로

- 반전증폭기 이득은 -1이고, 저역통과회로 뒤의 비반전증폭기 이득은  $1+R_1/R_1=2$ 이며, 저역통과함수를 사용하면 출력은 중첩성에 의해

$$\begin{split} V_o(j\omega) = &-V_i + 2\frac{1}{1+j\omega RC}\,V_i = \,V_i \left(-1 + \frac{2}{1+j\omega RC}\right) \!\! = V_i \!\left(\frac{1-j\omega RC}{1+j\omega RC}\right) \end{split}$$

라고 쓸 수 있음.

- 입력과 출력의 관계(전달함수):

$$\frac{V_o}{V_i}(j\omega) = \frac{1 - j\omega RC}{1 + j\omega RC}$$

- ▶ 크기: 분자와 분모는 서로 복소수 공액이므로 그들의 크기는 동일 (상수 1임)

- 위상각:  $\theta = -tan^{-1}(\omega RC/1) tan^{-1}(\omega RC/1) = -2tan^{-1}(\omega RC/1)$ ( $\omega \to 0$ 일 때  $\theta \to 0^o$ ,  $\omega \to \infty$ 일 때  $\theta \to -180^o$ )

또는

$$\theta=-2tan^{-1}(f/f_o)$$

이고 여기서  $f_o=1/2\pi RC$

$$f=f_o$$

일 때  $\theta=-2tan^{-1}(1)=-90^o$

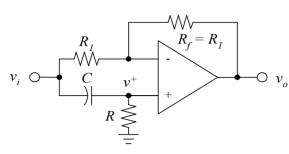

#### ㅁ진상(phase-lead)회로

- 출력전압에 대한 표현:

$$V_o(j\omega) = -V_i + 2\left(\frac{j\omega RC}{1+j\omega RC}\right)V_i$$

- 전달함수(transfer function):

$$\frac{V_o}{V_i}(j\omega) = \frac{-1 + j\omega RC}{1 + j\omega RC} = -1 \cdot \frac{1 - j\omega RC}{1 + j\omega RC}$$

- □ 크기: 1 (모든 주파수에서 입력과 출력의 진폭비가 1로 일정)

- 미 위상:  $\theta = 180^{\circ} tan^{-1}(\omega RC/1) tan^{-1}(\omega RC/1) = 180^{\circ} 2tan^{-1}(\omega RC)$

- 주파수가 영으로 접근할수록 위상은 180°로 접근

- 주파수가 증가함에 따라, 진상위상은 감소하고 최종적으로 영에 접근

- 위상을 주파수 f로 표현하면  $\theta=180^o-2tan^{-1}(f/f_o)$  임(여기서  $f_o=1/2\pi RC$ )  $f=f_o$ 일 때  $\theta=180^o-2tan^{-1}(1)=90^o$

- → 예제 11-5

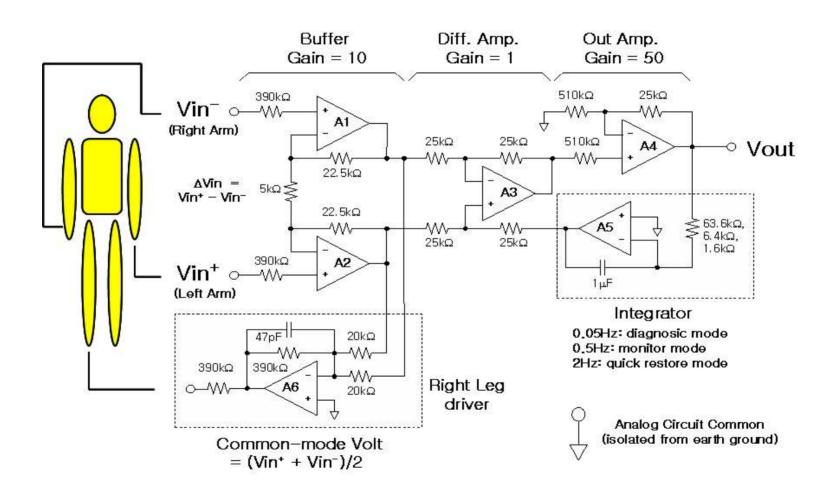

## ■ 계측 증폭기(Instrumentation amplifier)

#### ▶ Op amp를 이용한 기본적인 차동증폭기

< 기본적 Op-amp 차동증폭기 >

< 부동소스(floating source)를 가지는 Op-amp 차동증폭기 >

- 출력:

$$v_o = \frac{R_f}{R_1} \left( v_1 - v_2 \right) = \frac{R_f}{R_1} v_i$$

(중첩성 이용)

$$(\, \because \, ) \ \, v_o = - \, \frac{R_f}{R_1} v_2 + \left( 1 + \frac{R_f}{R_1} \right) \!\! \left( \frac{R_f}{R_1 + R_f} \right) \!\! v_1$$

#### <특징>

- 부동소스(floating source)에 의해 발생되는 신호전압을 증폭하기 위해 사용

- 이 구조는 잡음과 전자파의 간섭에 노출되어 긴 케이블을 통해 전달된 신호를 확대할 때 특히 유용

- 만약 두 신호선이 간섭에 동일하게 노출되었다면, 차동증폭기는 이를 제거하고 그 차이 신호만을 증폭

#### <결점>

- 차동입력저항은 대략  $2R_1$ 이므로, 이는 큰 값이 아님

- 차동증폭기의 공통모드제거는 저항들의 부정합(mismatch) 때문에 하나의 연산 증폭기 CMRR보다 작음 (각각의 입력선에 전압폴로워를 삽입한다면, 차동입력 저항은 매우 크게 만들 수는 있지만 CMRR의 감소는 개선하지 못함)

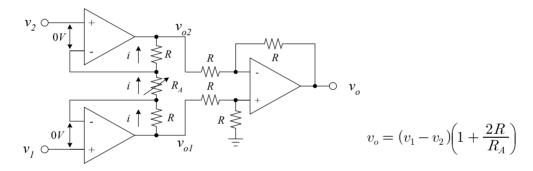

#### ▶ 개선한 차동증폭기(계측증폭기; IA)

- 각 입력신호가 Op amp의 비반전단자에 바로 연결되어지므로, 각 신호원에서는 매우 큰 입력저항으로 보임

- 이 회로는 계측증폭기(instrumentation amplifier: IA)라고도 하고, 단일-패키지 단 위로 판매되고 있음

- 이 소자들은 잘 정합된 고품질의 증폭기를 사용하고. 매우 큰 CMRR을 가짐

#### < 계측증폭기의 출력 >

- 각 입력증폭기의  $v_i^+$ 와  $v_i^-$ 는 서로 동일 $(v_i^+ v_i^- \approx 0)$ 하다고 가정

- 입력전압  $v_1$ 와  $v_2$ 는 가변저항  $R_4$ 의 양단에 나타남

- 분석목적을 위해  $v_1>v_2$ 이라고 가정할 때, 가변저항  $R_{\scriptscriptstyle A}$ 에 통해 흐르는 전류 i :

$$i = \frac{v_1 - v_2}{R_A} = \frac{v_{o1} - v_{o2}}{R_A + 2R}$$

- 출력차동단의 차동이득은 1이므로  $v_o = v_{o1} v_{o2}$

- 출력은 위의 두 식으로부터  $v_o = (v_1 v_2) \left( 1 + \frac{2R}{R_4} \right)$

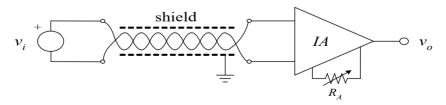

#### ▶ 계측증폭기의 가장 일반적인 응용

- 긴 케이블에 연결된 마이크로폰이나 열전대(Thermo-couple)에서와 같이, 잡음이 포함된 미약한 신호의 증폭

- 열전대는 감지할 온도에 비례하는 작은 dc전압(수 mV)을 발생시키는 공업용 센서로서, 그들은 2개의 리드선(+ 및 -)을 가지고 있으며 이들은 실드(shield)된 케이블에 연결되어 중앙제어장치나 온도측정기구와 접속

- 이 실드는 케이블에 전자기의 방해와 잡음을 줄이기 위해 접지시킴

- 신호원의 리드선 연결에서 발생한 잡음을 크게 감소시키기 위해서는, 차동증폭을 해야 함(신호원은 계측증폭기에 부동(floating)모드로 연결되어 있음)

#### ▶ 계측증폭기의 공통모드제거비(CMRR)

- CMRR: 공통모드이득 $(A_{cm})$ 에 대한 차동이득 $(A_d)$ 의 비

$$CMRR = \frac{A_d}{A_{cm}}$$

데시벨 표현:

$$CMRR_{dB} = 20\log\frac{A_d}{A_{cm}}$$

- 이상적인 차동증폭기는 영의 공통모드이득, 무한의 CMRR을 가져야 함

- 차동증폭기 공통모드이득  $A_{cm}$ 의 측정 방법

- 두 입력 단을 함께 묶고 상대적으로 큰 ac 전압(공급전압에 가까운)을 인가 예) 만약 공급전압이  $V_{CC}=\pm 15\,V$  이면 피크 입력전압이 약 14V 또는  $10V_{rms}$  이것은 단지 읽기 쉬운 출력전압을 얻기 위함

- 차동모드에서 부동신호(floating signal)를 증폭하기 위한 전형적인 연결

- 꼬인 리드선을 사용함으로써, 두 도체들은 외적인 교란에 동일하게 노출

- 실드는 "접지루프(ground loop)"라 불리는 것을 피하기 위해 단 한쪽 끝을 접 지시켜야 함. (접지루프는 IA에 의해 제거될 수 없는 전압이나 추가적인 잡음 을 발생시킬 수 있음)

- 차동 및 공통모드의 이득 모두를 안다면, 얼마나 많은 잡음신호가 계측증폭기에 의해 제거될 수 있는가를 결정할 수 있음

- 제조업체들은  $A_{cm}$ 의 값을 제공할 수 없음(사용자가 조정할 수 있는  $A_d$ 의 값에 의존하기 때문)  $\to$  제조업체는 dB로 CMRR을 명시함

- 신호성분 및 잡음성분의 출력

- 신호성분의 출력:  $v_{os} = A_d v_{is}$  (여기서  $v_{is}$ 는 입력신호성분)

- 잡음성분의 출력:  $v_{on} = A_{cm} v_{in}$  (여기서  $v_{in}$ 은 입력잡음성분)

$$v_{on} = A_{cm}v_{in}\frac{A_d}{A_{cm}}\frac{A_{cm}}{A_d} = v_{in}A_d\frac{A_{cm}}{A_d} = \frac{v_{in}A_d}{CMRR}$$

여기서의 CMRR은 dB가 아니므로 dB로 변환한 표현:  $v_{on} = \frac{A_d v_{in}}{10^{CMRR_{dB}/20}}$

#### ▶ 잡음비와 CMRR과의 관계

- CMRR을 알면 사용자가 출력신호에서의 잡음레벨 또는 더 중요한 출력신호에 대한 잡음비를 예측 가능하게 함

- 입력신호에 대한 잡음비 $(\mathit{SNR}_i)$ :  $\mathit{SNR}_i = v_{is}/v_{in}$

- 출력신호에 대한 잡음비 $(SNR_o)$ :  $SNR_o = v_{os}/v_{on}$

$$\rightarrow \frac{SNR_o}{SNR_i} = \frac{v_{os} \, v_{in}}{v_{is} \, v_{om}} = \frac{A_d}{A_{cm}} = CMRR \quad \text{Fig. SNR}_o = SNR_i \, (CMRR)$$

- ightarrow dB단위의 표현:  $SNR_o(dB) = SNR_i(dB) + CMRR_{dB}$

- $CMRR_{dB}$ 는 계측증폭기가 입력의 신호 대 잡음비  $SNR_{i}\left(dB\right)$ 의 개선효과를 제시

- 출력의 신호 대 잡음비 요구를 충족시키기 위한 계측증폭기의 최소 CMRR을 결 정하기 위한 설계방정식으로도 제공

- 예)  $SNR_i = -35dB$ 을 가지는 입력신호가 최소한 +60dB의  $SNR_o$ 을 가지도록 개선되 기 위해서는 계측증폭기는 적어도 95dB의 CMRR을 가져야만 함

#### ▶ 계측증폭기의 또 하나의 주요 응용

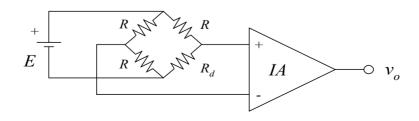

- 휘스톤브리지로 연결된 저항의 미세한 변화들을 탐지

- 수  $m\Omega$ 의 매우 작은 저항변화는 수 mV의 작은 전압변화를 발생시킴

- 계측증폭기는 전압계나 데이터획득시스템에 의해 이 작은 전압을 증폭시킴

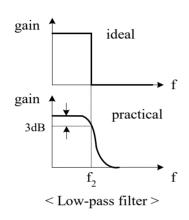

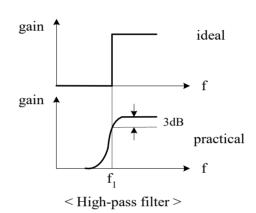

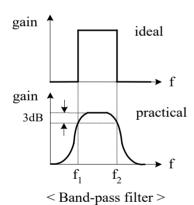

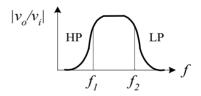

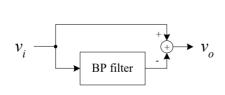

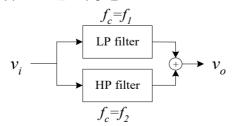

# ■ 능동필터

#### ㅁ 기초적인 필터 개념

- 필터: 어떤 영역의 주파수를 가지는 신호는 통과시키고, 다른 모든 신호들은 감 소시키는 장치

- → 필터들은 복합신호로부터 원하는 주파수성분들을 추출하거나, 잡음과 같은 원하지 않는 신호들을 제거하는 데 널리 사용

#### ▶ 필터의 종류:

• LPF, HPF, BPF, BRF(Notch 또는 BSF)

< Band-stop, notch, or band-reject filter >

- 수동필터(passive filter): 저항, 커패시터 및 인덕터 등의 수동소자로 구성

- 능동필터(active filter): 저항과 커패시터를 가진 회로망에 트랜지스터 및 연산 증폭기와 같은 능동소자들을 같이 사용

- ※ 인덕터는 크기, 비용 및 다양한 값의 부족으로 능동필터에 잘 사용되지 않음

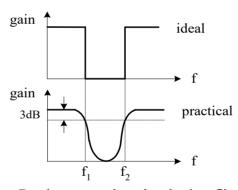

#### ▶ 필터의 분류

- 필터는 차수(order) 또는 극점(pole)의 수에 의해 분류

- 단순 RC회로망은 1차(first order) 또는 단일 극점(single-pole)필터라고 불리고, 그 응답은 저역통과유형에서 20dB/decade로 떨어짐

- 필터의 차수가 높을수록, 필터는 이상적인 필터에 접근하고 그것을 구성하기 위해 더욱 더 복잡한 회로설계가 요구됨

- 필터의 설계유형에 따른 분류

- 버터워스(Butterworth): 통과대역 내의 주파수에서 신호의 이득은 상대적으로 작은 변화를 가지기 때문에 최대평탄(maximally flat)필터라도 부름. (그림 11-30참조)

- 체비셰프(Chebyshev)필터: 통과대역 내에서는 버터워스 보다 더 큰 변화를 가지고 있지만 통과대역 밖에서는 더욱 가파른 기울기로 감쇄함. (그림 11-31참조)

- 대역통과필터는 Q(quality factor) 값에 의해 특성이 결정

$$Q = \frac{f_o}{BW}$$

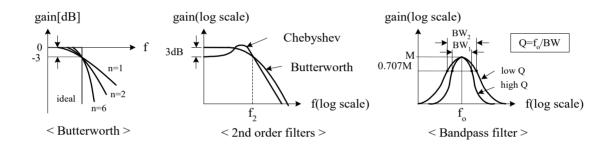

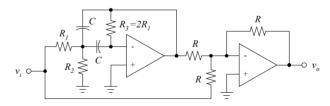

#### □ 능동필터설계

▶ 일반적인 구조

|                  | $Z_A$ | $Z_B$ | $Z_{\mathcal{C}}$ | $Z_D$ |

|------------------|-------|-------|-------------------|-------|

| Low-pass filter  | R     | R     | C                 | C     |

| High-pass filter | С     | C     | R                 | R     |

- 버터워스와 체비셰프 2차 LPF 및 HPF 설계에 모두 사용될 수 있음

- VCVS(전압제어전압원)구조를 가지고, Sallen-Key회로라 부름

- 필터의 차수(극점의 수)가 홀수이면, 여분의 1차(first-order)블록이 필요

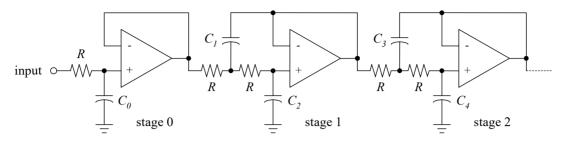

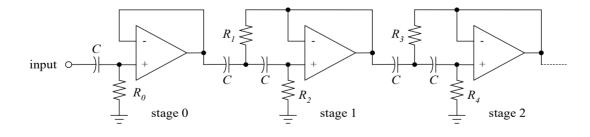

#### □ 저역통과필터

▶ 저역통과필터를 사용할 일반적인 구조

- 5차 LPF: 단계 0의 1차 블록과 2개의 2차 Sallen-Key단을 직렬연결 홀수 차수의 필터만이 1차수 블록이 필요

- 표 11-2를 이용하여 R 및 C값을 결정 (R값을 결정한 후 C값을 결정)

예제 11-9) 차단주파수가  $2.5 \mathrm{kHz}$ 인 3차 저역통과 버터워스필터를 설계하라.  $R=10k\Omega$ 로 선택하라.

#### 풀이

표 11-2로부터,  $a_0=1, a_1=1, a_3=1$ 을 구할 수 있고, 저역통과공식에 대입하면,

$$C_0 = \frac{1}{2\pi(2.5k)(10k)} = 6.37nF$$

$$C_1 = \frac{1}{\pi(2.5k)(10k)} = 12.7nF$$

$$C_2 = \frac{1}{4\pi(2.5k)(10k)} = 3.18nF$$

과 같다.

#### □ 고역통과필터

- ▶ 고역통과필터의 일반적인 구조

- 표 11-2를 이용하여 R 및 C값을 결정 (C값을 결정한 후 R값을 결정)

예제 11-10) 차단주파수가 800Hz, 2-dB의 리플을 가지는 단위이득의 4차 고역통과 체비셰프필터를 설계하라. C=100nF로 선택하라.

#### 풀이

표 11-2로부터,  $a_1=0.20977, a_2=0.92898, a_3=0.50644, a_4=0.22157을 구할 수 있다. 고역통과공식에 대입하면,$

$$\begin{split} R_1 &= \frac{0.20977}{4\pi(800)(100nF)} = 208.7 \varOmega \\ R_2 &= \frac{0.92868}{\pi(0.20977)(800)(100nF)} = 17.62 k \varOmega \\ R_3 &= \frac{0.50644}{4\pi(800)(100nF)} = 503.8 \varOmega \\ R_4 &= \frac{0.22157}{\pi(0.50644)(800)(100nF)} = 1.741 k \varOmega \end{split}$$

과 같다.

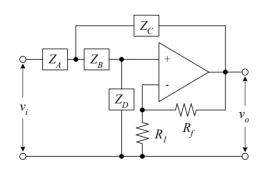

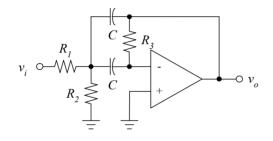

#### □ 단순 대역통과필터

▶ IGMF(infinite-gain multiple-feedback) 필터

$$BW = \frac{1}{\pi R_3 C}$$

$$G_o = \frac{R_3}{2R_1}$$

$$f_o = \frac{1}{2\pi C\sqrt{(R_1 \parallel R_2)R_3}}$$

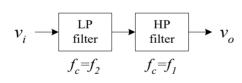

▶ LPF 및 HPF를 이용한 BPF

# ㅁ 대역저지필터(Band stop filter)

▶ LPF 및 HPF를 이용한 BSF

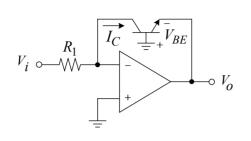

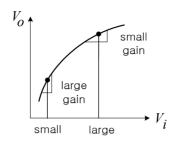

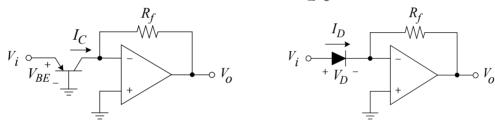

# ■ 로그증폭기 (Logarithmic Amplifier)

- 로그증폭기: 입력의 로그에 비례하는 출력을 발생

- ▶ 로그증폭기의 주요 응용

- 1) 넓은 생동폭(dynamic range)를 가지고 있는 신호에 대한 증폭

- 매우 큰 신호와 매우 작은 신호를 모두 가지고 있는 신호에 대한 증폭

- 예) 온도 센서는 매우 낮은 온도에서 수 mV. 매우 높은 온도에서 수 V를 발생

- → 좋은 분해능을 가지기 위해서는 작은 신호에 대해 증폭하고 큰 신호는 이득을 감소시킴

- 2) 신호의 전압을 곱하거나 나누는 아날로그 계산

- 예 1) 두 입력전압의 곱  $v_1v_2$ 을 발생

- 두 입력 각각에 로그증폭하고 이들을 합함 :  $\log[v_1] + \log[v_2] = \log[v_1v_2]$

- 역로그증폭기의 입력에  $\log[v_1v_2]$ 를 인가하여 출력 :  $v_1v_2$ 에 비례하는 전압

- 예 2) 나누기:  $\log[v_1] \log[v_2] = \log[v_1/v_2]$   $\rightarrow$  역로그 취하면  $v_1/v_2$

- ▶ 로그증폭기의 출력전압 유도

- BIT의 컬렉터전류와 베이스-에미터 전압과의 관계:

$$I_C = I_S \left( e^{V_{BE}/V_T} - 1 \right) \approx I_S \; e^{V_{BE}/V_T}, \qquad \left( e^{V_{BE}/V_T} \gg 1 \,

ight)$$

라 가정)

- 양변에 로그를 취하고  $V_{BE}$ 에 대해 풀면  $V_{BE} = V_T \ln (I_C/I_S)$

- 컬렉터는 가상접지 $(\approx 0\,V)$ 이므로  $I_C=V_i/R_1$  또한  $V_{BE}=-V_o$ 이므로

$$V_o = -V_T \ln \left( \frac{V_i}{I_S R_1} \right)$$

- 상용로그와 자연로그와의 관계는  $\ln x = 2.303 \log_{10} x$  이므로

$$V_o = -2.303 V_T \log_{10} \left( \frac{V_i}{I_S R_1} \right)$$

- 상온에서  $V_T pprox 0.0257[V]$  이므로

$$V_o = -0.0257 \ln \left( \frac{V_i}{I_S R_1} \right) = -0.0592 \log_{10} \left( \frac{V_i}{I_S R_1} \right)$$

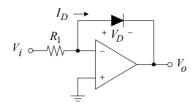

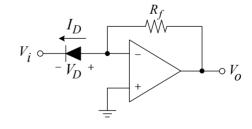

▶ 다이오드를 이용한 로그증폭기

$$I_D = I_S \left( e^{V_D/V_T} - 1 \right) \approx I_S \; e^{V_D/V_T}, \qquad (e^{V_D/V_T} \gg 1$$

이라 가정)

$$V_D = V_T \ln(I_D/I_S)$$

이고,  $V_o = -V_D$  이므로

$$V_o = -V_D = -V_T \ln(I_D/I_S)$$

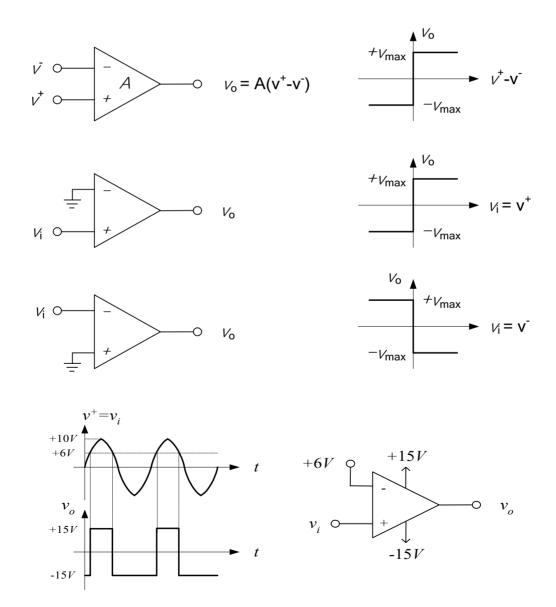

# ■ 지수(또는역로그)증폭기

- 지수(exponential or anti-logarithmic) 증폭기: 입력의 지수에 비례하는 출력을 발생

$$\begin{split} I_C &= I_S \left( e^{V_{BE}/V_T} - 1 \right) \approx I_S \; e^{V_{BE}/V_T} \\ V_{BE} &= V_i \quad \mathbb{R} \quad V_o = -I_C R_f \; \text{이므로} \\ V_o &= -I_S R_f \, e^{V_i/V_T} \\ \end{split} \quad \begin{split} I_D &= I_S \left( e^{V_D/V_T} - 1 \right) \approx I_S \; e^{V_D/V_T} \\ V_D &= V_i \quad \mathbb{R} \quad V_o = -I_D R_f \; \text{이므로} \\ V_o &= -I_S R_f \, e^{V_i/V_T} \\ \end{split}$$

$$I_D = I_S \left(e^{V_D/V_T} - 1\right) \approx I_S \; e^{V_D/V_T}$$

$$V_D = V_i \quad 뭐 \quad V_o = -I_D R_f \;

ho$$

므로

$$V_o = -I_S R_f \, e^{V_i/V_T}$$

$$\begin{split} I_C &= I_S \left( e^{V_{BE}/V_T} - 1 \right) \approx I_S \; e^{V_{BE}/V_T} & I_D = I_S \left( e^{V_D/V_T} - 1 \right) \approx I_S \; e^{V_D/V_T} \\ V_{BE} &= -V_i \quad 및 \quad V_o = I_C R_f \; \text{이므로} & V_D = -V_i \quad 및 \quad V_o = I_D R_f \; \text{이므로} \\ V_o &= I_S R_f \; e^{V_i/V_T} & V_o = I_S R_f \; e^{V_i/V_T} \end{split}$$

$$I_D = I_S \left( e^{V_D/V_T} - 1 \right) \approx I_S e^{V_D/V_T}$$

$$V_D = -V_i \quad 및 \quad V_o = I_D R_f \text{ 이므로}$$

$$V_o = I_S R_f e^{V_i/V_T}$$

# Chap. 12 Wave generation and shaping

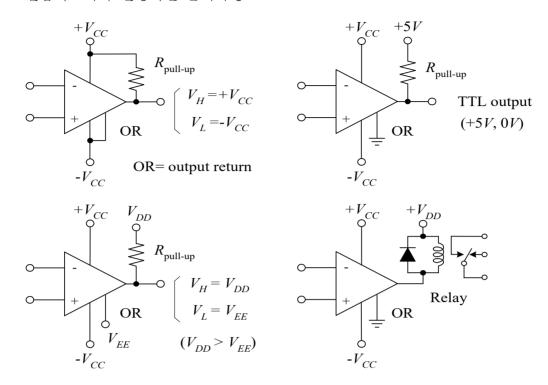

## ■ Voltage comparator (전압비교기)

- 2개의 입력전압레벨을 비교하기 위해 사용되는 소자

- 한 입력이 다른 입력보다 더 클 때는 높은 출력을, 다른 입력이 더 클 때는 낮 은 출력을 발생시킴

- 연산증폭기에서와 매우 유사한, 높은 이득의 차동입력단을 가짐

- 출력단은 단지 2개의 전압레벨만으로 출력되게 설계 (출력은 사실상 디지털값)

- 전압비교기는 아날로그부와 디지털부를 인터페이스하는 가장 간단한 형태임

- 신호검출, 경보시스템, 제어 및 멀티바이브레이터 등에 응용

▶ 전압비교기의 전형적인 출력특성

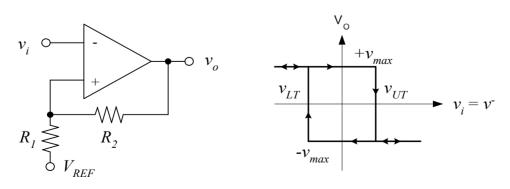

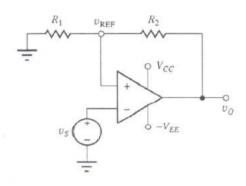

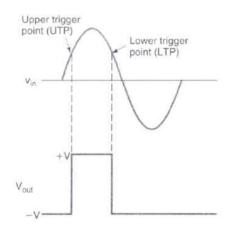

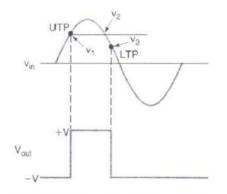

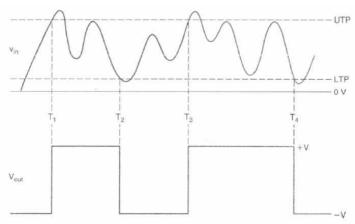

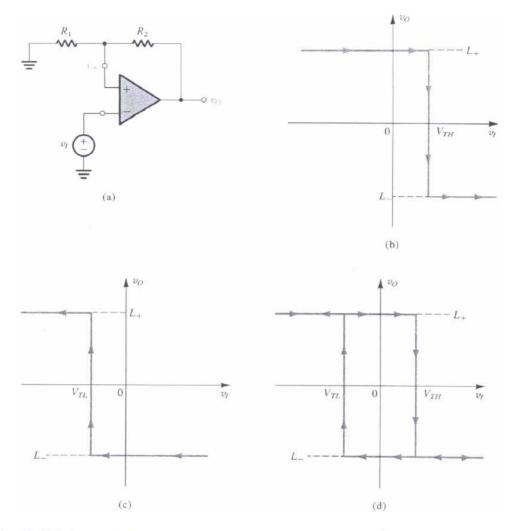

## ㅁ 히스테리시스와 슈미트트리거

- 히스테리시스(hysteresis): 어떤 소자가 입력이 증가할 때와 감소할 때에 서로 달리 동작하는 특성을 의미함

- 전압비교기의 히스테리시스: 입력이 한 레벨로 증가하면 출력은 스위칭될 것이지 만, 그 입력이 동일 레벨을 지나 다른 레벨로 감소할 때 까지 출력이 역으로 스위칭되지 않는 것을 의미함

- 비교기 히스테리시스특성의 이용 입력의 랜덤한 잡음파동으로 인한 응답으로 급속한 채터링 스위칭을 방지함

- ▶ 히스테리시스를 가지는 전압비교기(슈미트트리거)

- $v_i$ 가 하위 트리거레벨 $(V_{LT})$  아래로 떨어질 때  $V_H$ 로 전환

- $v_i$ 가 상위 트리거레벨( $V_{UT}$ )을 지나 상승할 때 까지는  $V_L$ 로 전환하지 않음

- 화살표들은 입력이 증가할 때(상위 라인)과 감소할 때(하위 라인)에 따른 특성을 나타냄

- 이 특성을 가지고 있는 비교기를 슈미트트리거(schmitt trigger)라고 함

- 히스테리시스 전압 유도

- (+) 입력단 전압  $v^+$ 를 구하기 위해 중첩의 원리를 사용

i)

$$v_o=0$$

일 때 :  $v^+={R_2\over R_1+R_2}\,V_{REF}$   $\left(v_o=0\,\right)$

ii)

$$v_{REF}=0$$

일 때 :  $v^+={R_1\over R_1+R_2}v_o$   $(V_{REF}=0)$

iii) 두 전압을 동시에 인가할 때:

$$v^+ = \frac{R_2}{R_1 + R_2} \, V_{REF} \, + \frac{R_1}{R_1 + R_2} \, (v_o)$$

- $v_o$ 가 2개의 가능한 값  $V_H$ 와  $V_L$ 을 가지기 때문에,  $v^+$ 도 2개의 값을 가짐

- 트리거레벨  $V_{UT}$  및  $V_{LT}$  :

$$V_{LT} = \frac{R_2}{R_1 + R_2} V_{REF} + \frac{R_1}{R_1 + R_2} (V_L)$$

$$V_{LT} = \frac{R_2}{R_1 + R_2} V_{REF} + \frac{R_1}{R_1 + R_2} (V_L)$$

$$V_{UT} = \frac{R_2}{R_1 + R_2} V_{REF} + \frac{R_1}{R_1 + R_2} (V_H)$$

• 슈미트트리거의 히스테리시스 전압 $(V_{hus})$ :

$$\begin{split} V_{hys} &= \ V_{UT} - \ V_{LT} = \left(\frac{R_1}{R_1 + R_2}\right) \!\! \left( \ V_{\!H} \right) - \left(\frac{R_1}{R_1 + R_2}\right) \!\! \left( \ V_{\!L} \right) \\ &= \frac{R_1}{R_1 + R_2} \left( \ V_{\!H} - \ V_{\!L} \right) \end{split}$$

- 예제 12-1과 12-2 참조

## ■ 멀티바이브레이터 (Multivibrator) 및 파형정형 (waveshaping)

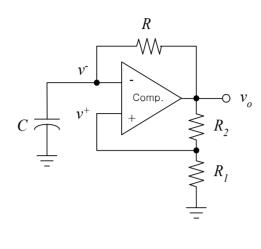

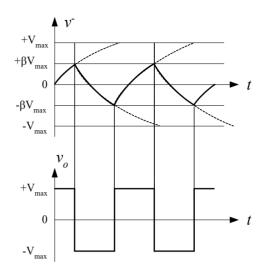

- □ 비안정 멀티바이브레이터 (Astable multivibrator)

- 비안정(astable)은 불안정(unstable)을 의미하고 비안정 멀티바이브레이터는 구형 파 발진기임

- 비교기의 출력전압들은 크기가 같고 극성이 반대 즉,  $\pm V_{

m max}$ 이라고 가정

- 출력이  $+ V_{\max}$ 일 때, 비반전입력에서 귀환되는 전압:

$$v^{+} = \frac{R_{1}}{R_{1} + R_{2}} V_{\text{max}} = + \beta V_{\text{max}}$$

- $v^-$ 는 커패시터 양단의 전압이며, 커패시터는 +  $V_{\rm max}$ 의 최종적인 전압 쪽으로 저항 R을 통해 충전하기 시작

- 커패시터전압이  $v^+$ 와 같은 전압에 도달할 때 즉,  $v^- = v^+ = + \beta V_{\rm max}$ 인 지점에서 스위칭이 발생 (출력은  $-V_{\rm max}$ 이 됨)

- 출력이  $-V_{

m max}$ 일 때, 비반전입력으로 귀환된 전압 :

$$v^{+} = \frac{R_{1}}{R_{1} + R_{2}} \left( - \ V_{\text{max}} \right) = - \beta \, V_{\text{max}}$$

- 비교기의 출력은 현재 음이기 때문에, 커패시터는  $-V_{

m max}$  쪽으로 저항 R을 통해서 방전하기 시작

- 방전되는 전압이  $-\beta V_{\rm max}$ 로 떨어질 때, 다시  $v^-=v^+$ 가 되어 비교기는  $+V_{\rm max}$ 로 스위칭되어 복귀

- ▶ 멀티바이브레이터 발진의 주기 :

- $v^-(t) = v_c(t)$ 가  $-\beta V_{\text{max}}$ 에서 +  $V_{\text{max}}$ 로 충전될 때의 시간함수:

$$v_c(t) = \, V_{\rm max} + (-\,\beta \, V_{\rm max} - \, V_{\rm max}) e^{-t/\!RC} = \, V_{\rm max} \left[ 1 - (1+\beta) e^{-t/\!RC} \, \right]$$

• t=T/2에서  $v_c(t)=+\beta V_{\max}$ 이므로

$$T = 2RC \ln \left(\frac{1+\beta}{1-\beta}\right) \qquad \text{ $\Xi$ $\stackrel{\sim}{=}$ } \qquad T = 2RC \ln \left(1+\frac{2R_1}{R_2}\right)$$

• T는  $V_{

m max}$ 에 무관함

# ㅁ 파형정형 (Waveshaping)

- 파형정형: 원하는 모양을 가지는 새로운 파형을 발생시키기 위해 몇몇의 규정된 방법으로 파형의 모양을 변경하는 과정

- 예) 구형파를 발생하기 위해 삼각파를 변경, 그 반대로 변형 사인파를 발생하기 위해 구형파나 삼각파를 변경 구형파를 발생하기 위해 사인파를 변경

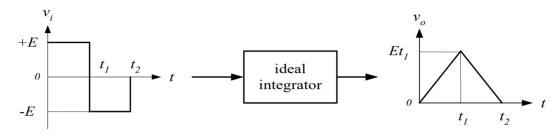

#### ▶ 적분기를 사용한 삼각파형의 발생

- 이상적인 적분기

- 적분기를 사용한 삼각파형의 발생

- $V_i = E$ 일 때  $V_o = -\frac{1}{R_1C} \int_0^t E \ dt = -\frac{E}{R_1C} t$  이므로 삼각파의 기울기는  $-E/R_1C$  [V/sec]이고,  $V_i = -E$ 일 때  $+E/R_1C$  [V/sec]임.

- 구형파의 주기를 T모 표현할 때, 삼각파의 피크값은 t = T/4일 때의  $V_a$ 값임.

$$V_{pk} = \frac{ET}{4R_1C}$$

- ightarrow 주기  $\mathrm{T}$ 가 증가(주파수가 감소)에 따라 삼각파의 진폭은 증가 주파수 증가는 전압이 변화하는 시간  $\triangle t$  및 전압의 변화  $\Delta V$ 를 감소시킴

- 입력에 dc성분이 있을 때 출력 dc성분 :

$$V_o(dc) = \frac{-R_f}{R_1} V_i(dc)$$

$\rightarrow$  삼각파의 출력은  $V_o(dc)$ 와 같은 양에 의해 위 또는 아래로 이동

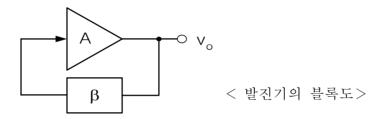

## ■ 발진기(oscillator)

- 발진기: 입력신호가 없이 스스로 주기적인 ac 출력신호를 발생하는 장치

- 발진기는 사인파 신호발생기를 주로 의미함

- 구형파 발생기는 보통 멀티바이브레이터라고 부름

#### ◆ 바크하우젠 조건 (Barkhausen Criterion)

- 발진기는 입력을 가지지 않고 폐회로로 구성

- 궤환은 루프 내의 어디에서나 시작할 수 있고 모든 위치가 입출력일 수 있음

- 모든 발진기는 저항성의 손실을 보충하고 발진을 지속시키기 위해 에너지를 공급하는(dc전원으로부터) 증폭기 또는 소자를 가져야만 한다.

- 바크하우젠 조건:  $A\beta = 1$

- $\rightarrow$  시스템이 발진하기 위해서, 루프이득  $A\beta$ 가 1이어야 함

- 주파수에 대한 루프이득의 복소수 페이서:

$$A\beta(j\omega) = |A\beta| \cos\theta + j |A\beta| \sin\theta$$

- $\rightarrow$  발진조건 (바크하우젠 조건) :  $|A\beta|=1$  및  $\theta=\pm360\,{}^{\circ}n$

- 일반적으로, 이득 크기가 1이고, 동시에 전체 위상이동은 0°(동상, 360°의 배수) 인 주파수는 오직 한 개임

- → 이와 같은 조건들을 만족하는 주파수로 발진

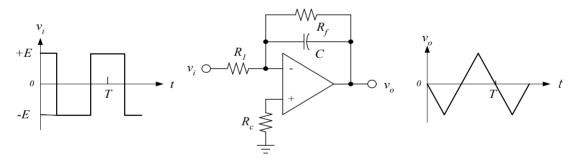

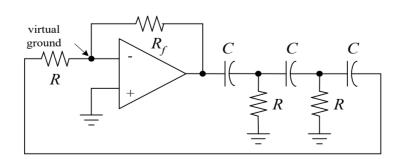

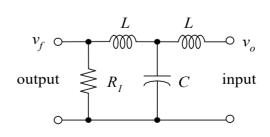

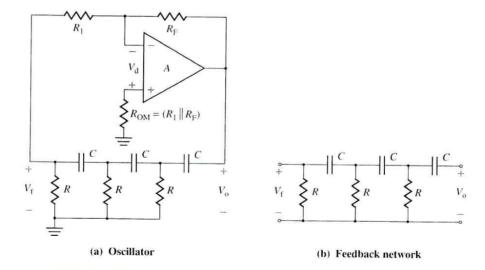

## □ RC 위상이동 발진기

- 증폭기가 반전구조로 연결되고 3개의 종속 접속된 RC부(고역통과)로 구동

- 반전증폭기: 신호의 위상을 180°로 이동

- 종속 접속된 RC부: 위상을 180°로 이동

- → 전체 위상이 180°로 이동, 루프이득은 1

- 단일 고역통과 RC회로망의 출력은 위상각이 입력보다 앞섬

- 신호가 3개의 RC부를 통해 지나갈 때. 위상이 180°로 이동하는 주파수에서 발진

- RC 종속접속 내에서 손실을 만회하여 루프이득이 1이 되기 위해 필요한 이득은 증폭기에 의해 공급 (증폭기의 이득:  $-R_f/R$ )

- ▶ RC 종속접속에 의해 결정되는 궤환율:

$$\beta = \frac{R^3}{(R^3 - 5RX_C^2) + j(X_C^3 - 6R^2X_C)}$$

- ▶ 발진주파수

- 발진이 될 때 궤환율 β의 각이 180°이므로 β는 순수한 실수임

- β의 식에서 분모의 허수부를 0으로 두고 ω에 대해 풀면 발진주파수를 구할 수 있음

$$X_C^3 - 6R^2 X_C = 0$$

$$X_C^3 = 6R^2 X_C$$

$$X_C^2 = 6R^2$$

$$\frac{1}{(\omega C)^2} = 6R^2$$

$$\omega_0=rac{1}{RC\sqrt{6}}$$

또는  $f_0=rac{1}{2\pi\sqrt{6}RC}$  <발진주파수>

ightharpoonup 발진주파수  $ω_o$ 에서 β의 이득감소값

$$\beta \mid_{\omega_o} = \frac{R^3}{R^3 - 5RX_C^2}$$

$$= \frac{R^3}{R^3 - 30R^3} \qquad (\because) X_C^2 = 6R^2$$

$$= -1/29$$

- ▶ 증폭기의 이득 *A*

- $\omega_o$ 에서 eta의 이득이 -1/29이므로 루프이득 Aeta=1이 되기 위해 A=-29

$$\therefore \quad \frac{R_f}{R} = 29 \quad \text{FE } R_f = 29R$$

예제 12-6) 100Hz에서 발진하는 RC 위상이동 발진기를 설계하라.

풀이

$$f=100Hz=\frac{1}{2\pi\sqrt{6}RC} \circ ] \text{고}, \ C=0.5\mu F \circ ]$$

라 두면,

$$R=\frac{1}{100\left(2\pi\right)\sqrt{6}\left(0.5\times10^{-6}\right)}=1300\Omega$$

$$R_f=29R=29\left(1300\Omega\right)=37.7k\Omega$$

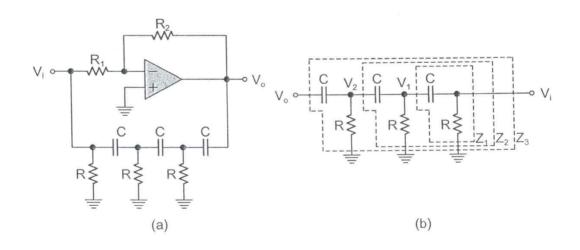

### □ 빈 브리지(Wien bridge) 발진기

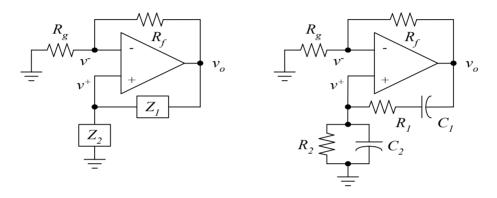

- $Z_1$  및  $Z_2$ 라고 명칭된 임피던스 블록들은 궤환율을 결정하는 전압분배기를 형성

- 출력전압의 일부가 이 임피던스 분배기를 통해 증폭기의 +입력으로 궤환

- 저항  $R_a$  및  $R_t$ 는 증폭기 이득을 결정

- 루프이득이 1이 되도록 임피던스가 선택된다면, 증폭기의 입력  $(v^+)$ 에 궤환되는 신호의 위상이동이 영이 되는 어떤 주파수가 존재

- ▶ RC망을 사용한 빈브리지 발진기

- $Z_1$  (RC직렬):  $Z_1=R_1-jX_{C_1}$

- $Z_2$  (RC병렬) :  $Z_2 = R_2 \parallel -j X_{C_2} = \frac{-j R_2 X_{C_2}}{R_2 j X_{C_3}}$

• 제한 한 :

$$\beta = \frac{v^+}{v_o} = \frac{Z_2}{Z_1 + Z_2} = \frac{-jR_2X_C/(R_2 - jX_C)}{R_1 - jX_{C_1} - jR_2X_{C_1}/(R_2 - jX_{C_2})} = \frac{R_2X_C}{(R_1X_{C_2} + R_2X_{C_1} + R_2X_{C_1}) + j(R_1R_2 - X_{C_1}X_{C_2})}$$

$v^+$ 가  $v_o$ 과 같은 위상을 가지기 위해서는, 이 비율은 실수여야 함(허수부는 0)

• 발진주파수  $\omega_o$  : 허수부가 0이 되는 주파수

$$\begin{split} R_1 R_2 - X_{C_1} X_{C_2} &= 0 & \rightarrow & R_1 R_2 &= \left(\frac{1}{\omega C_1}\right) \left(\frac{1}{\omega C_2}\right) \\ \omega_o^2 &= \frac{1}{R_1 R_2 C_1 C_2} & \stackrel{\text{H-}}{=} & \omega_o &= \frac{1}{\sqrt{R_1 R_2 C_1 C_2}} \end{split}$$

• 대부분의 응용에서는  $R_1=R_2=R$  및  $C_1=C_2=C$ 이 되게 만들며, 이 경우의 발진주파수 :

$$\omega_o = \frac{1}{\sqrt{R^2 C^2}} = \frac{1}{RC} \qquad \text{Fig. } f_o = \frac{1}{2\pi RC}$$

•  $R_1 = R_2 = R$  및  $C_1 = C_2 = C$  일 때, 발진주파수에서 각 커패시터의 용량성 리액턴스 :

$$X_{C_1} = X_{C_2} = \frac{1}{\omega_o C} = \frac{1}{\left(\frac{1}{RC}\right)C} = R$$

•  $X_{C_1} = X_{C_2} = R = R_1 = R_2$ 일 때, 발진주파수에서의 궤환율 :

$$\frac{v^+}{v_o} = \frac{R^2}{3R^2 + j0} = \frac{1}{3}$$

• 루프이득이 1이 되기 위해서는 증폭기의 이득은 3이 되어야 함. 증폭기의 이득은  $1+R_f/R_g$ 이므로

$$1 + \frac{R_f}{R_q} = 3 \rightarrow \frac{R_f}{R_q} = 2$$

※ 연산증폭기가  $v^+\approx v^-$ 이라는 특성을 이용하면,  $v^-=v_oR_g/(R_g+R_f)$ 이므로  $v^-/v_o=R_g/(R_g+R_f)=v^+/v_o=1/3$ 이라는 것을 알 수 있음

예제 12-7) 25kHz에서 발진하는 빈 브리지 발진기를 설계하라.

풀이  $C_1 = C_2 = 0.001 \,\mu F$ 라고 하면, 식으로부터

$$f=25 imes10^3 Hz=rac{1}{2\pi R\left(10^{-9}F

ight)}$$

$$R=rac{1}{2\pi\left(25 imes10^3 Hz

ight)\left(10^{-9}F

ight)}=6366 \Omega$$

과 같다.

$R_{\!\scriptscriptstyle g}=10k\Omega$  이라고 하면, 식으로부터

$$\frac{R_f}{R_a} = 2 \rightarrow R_f = 20k\Omega$$

을 구할 수 있음.

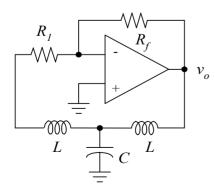

### ㅁ 콜피츠 발진기(Colpitts oscillator)

- 궤환회로 내의 임피던스는 저역통과 LC회로망 (위상이동이 180°)

- 발진주파수는 회로망을 통한 위상이동이 180°인 주파수임

- 부하가  $R_{\scriptscriptstyle 1}$ (반전증폭기의 가상접지로 인한)인 궤환회로망 $(\beta$ 망)의 전달특성함수

$$\beta = \frac{1}{(1-\omega^2 LC) + j\left(\frac{2\omega L - \omega^3 L^2 C}{R}\right)}$$

$\rightarrow \beta$ 가 실수이기 위해, 허수부는 0이어야 하므로

$$2\omega L = \omega^3 L^2 C \rightarrow \omega_o^2 L C = 2$$

- 발진주파수:  $f_o = \frac{1}{2\pi\sqrt{LC/2}}$

- $\omega_o^2 LC = 2$ 인 조건에서

- i)  $\beta = -1 \rightarrow \beta$ 망을 통해  $180^{\circ}$ 의 위상이동이 일어남

- ii) 증폭기 이득 = -1  $\rightarrow$   $R_f=R_1$

- 실제적인 설계에서의 고려사항  $\beta$ 망의 선택도(Q factor)가 너무 낮거나 너무 높지 않도록 설정  $(2\sim 10$ 이 적절)  $Q=R_1\sqrt{C/L}$

예제 12-8) 100kHz에서 발진하는 콜피츠 발진기를 설계하라.

풀이

$$R_1=R_f=5k\Omega$$

및  $C=0.001\mu F$ 로 선택하면 식으로부터

$$L=\frac{2}{(2\pi)^2f_o^2C}=\frac{2}{(2\pi)^2(100\times 10^3 Hz)^2(0.001\times 10^{-6}F)}\approx 5mH$$

을 구할 수 있고, Q를 검사하면

$$Q = 5k\sqrt{\frac{1nF}{5mH}} \approx 2.2 \ (OK)$$

과 같다.

# □ 하틀리 발진기(Hartley oscillator)

- $-\beta$ 회로망은 2개의 커패시터와 <math>1개의 인덕터로 구성된 고역통과 LC회로망

- 발진주파수 ( $\beta$ 함수가 실수인 주파수) :  $f_o = \frac{1}{2\pi\sqrt{2LC}}$

- 하틀리 발진기의 "Q"는 콜피츠 발진기의 것과 동일함

### ■ 8038 집적회로 함수발생기

- 정현파, 삼각파 및 구형파를 발생시킬 수 있는 함수발생기 IC

- ICL8038은 Intersil에 의해 제조된 것이고 다른 제조업체에서도 제조되어 시판

- 0.0001Hz에서 1MHz까지의 주파수 범위에 걸쳐 3개의 파형들을 동시에 발생

- 주파수는 외부에서 연결된 저항과 커패시터의 조합으로 결정

$$f_o = \frac{0.15}{RC}$$

- 주파수는 외부의 전압에 의해 제어될 수도 있음.

- → 전압제어 발진기(VCO; voltage controlled oscillator)로 동작

### ■ 클리핑과 정류회로

### ㅁ 클리핑회로

- 파형정형 및 비선형 함수발생을 위해 파형의 진폭을 의도적으로 자르는데 사용

### □ 정밀 정류회로

- 전원공급기의 응용에 있어서 입력전압이 상당히 높기 때문에 다이오드의 0.7V 전압강하는 큰 문제가 되지 않음

- 계측기에서 다이오드의 0.7V 전압강하는 전체 입력전압 진폭값에 대해 큰 값일수 있고, 회로의 동작에 심각한 영향을 줄 수도 있음

- → 이들 응용을 위해 정밀정류기가 필요

### ■ 클램핑회로(clamping circuit)

- ac신호에 dc레벨을 더 함으로써 ac파형을 위 또는 아래로 이동하는 데 사용

- 레벨이동(level shift)이 더 좋은 표현임

# 강의 보조 자료

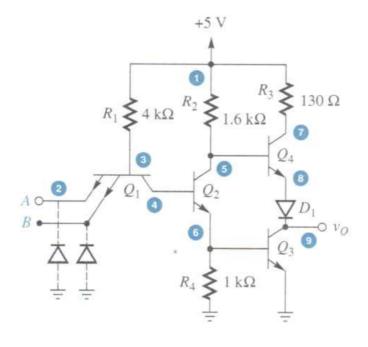

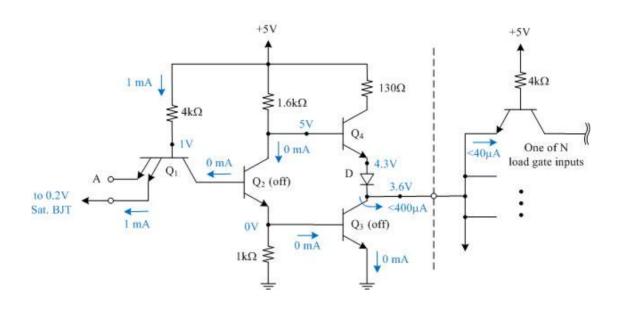

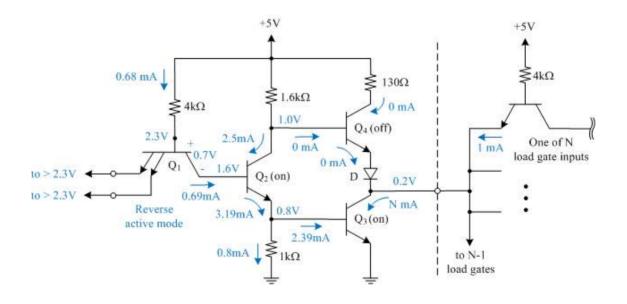

# TTL(Transistor-Transistor Logic) NAND 회로

| INPUT |   | OUTPUT |

|-------|---|--------|

| A     | В | OUIPUI |

| 0     | 0 | 1      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 0      |

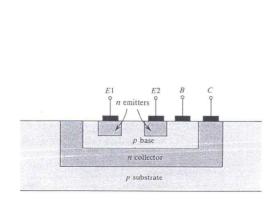

$< Q_{\!\scriptscriptstyle 1}$ 의 반도체 구성도>

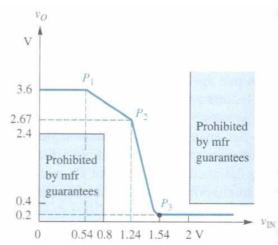

<입출력 전달특성>

■ 두 입력(A, B) 중 하나라도 Low(0.2V)일 때 출력은 High

■ 두 입력 모두 High(2.3V 이상)일 때 출력은 Low

# 라인트레이서 (Line tracer)

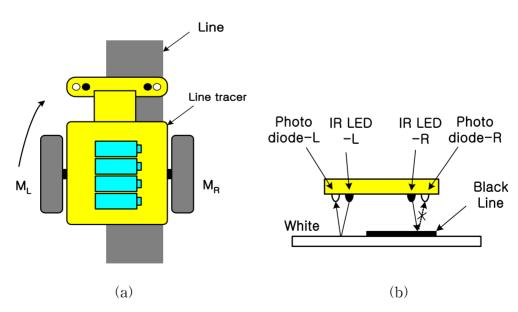

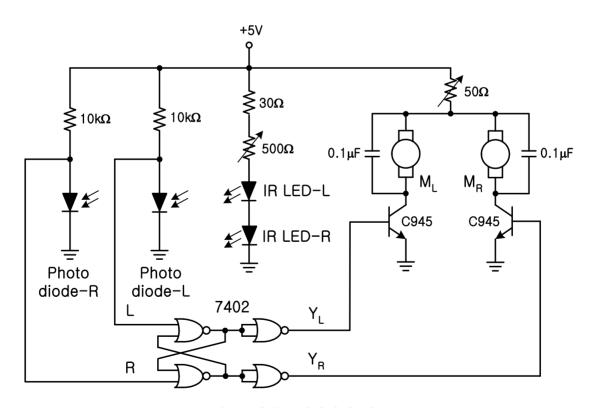

라인트레이서는 백색의 바닥에 그려진 흑색의 라인(line)을 따라 주행하는 로봇을 의미한다. 그림 1은 라인트레이서 한 예의 외형을 나타낸다. 라인트레이서는 IR LED에서 조사된 빛이 바닥 또는 라인에 반사되어 광다이오드(photo diode)에 수광되도록 설치되었다. 백색은 빛을 잘 반사하고 흑색은 빛을 흡수하므로, 라인은 반사광의 강도에 따라 검출한다. IR LED와 광다이오드는 하나의 짝(pair)을 이루어 2개이상의 짝으로 구성된다. 그림 2는 2개의 IR LED와 광다이오드 짝으로 구성된 라인트레이서의 구성도이다.

그림 1. 라인트레이서의 외형

그림 2. 라인트레이서의 개요도, (a) 윗면 및 (b) 후면

그림 2(a)는 위에서 바라본 형태로서 백색 바닥의 흑색 라인위에 높여진 라인트 레이서를 나타낸다. 전면부에는 라인검출을 위한 센서부로서 2짝의 IR LED와 광다이오드가 배치되었다. 그림 2(b)는 후면에서 바라 본 센서부를 나타낸다. 좌측의 센서짝(Photo diode-L과 IR LED-L)은 백색 바닥에 위치하여 수광된 빛의 세기가 강하고, 우측의 센서짝(Photo diode-R과 IR LED-R)은 흑색 라인에 위치하여 수광된 빛의 세기가 약하다. 이 경우에는 라인트레이서가 라인의 좌측으로 치우쳐 있으므로 좌측바퀴용 모터( $M_L$ )을 구동시키고 우측바퀴용 모터( $M_R$ )을 정지시켜 라인트레이서가 우측으로 회전하도록 회로가 설계되어야 한다.

그림 3은 라인트레이서의 구동 회로도를 나타낸다. 2개의 IR LED-L과 IR LED-R의 강도는 가변저항  $500\Omega$ 로 조정된다. 바닥에서 반사된 빛은 광다이오드에 수광되며, 빛이 강할 때는 광다이오드가 도통되어 낮은 전압이 되고 빛이 약할 때는 광다이오드가 차단되어 높은 전압으로 이진화된 전압이 된다. 이들의 전압은 7402 논리회로를 통해 트랜지스터의 입력에 각각 인가된다. 트랜지스터는 스위칭되어 모터  $M_L$ 과  $M_R$ 을 구동시킨다. 가변저항  $50\Omega$ 은 모터의 속도를 조정하기 위해 사용된다.

그림 3. 라인트레이서의 회로도

LF353 Wide Bandwidth Dual JFET Input Operational Amplifier

### **LF353**

# Wide Bandwidth Dual JFET Input Operational Amplifier

### **General Description**

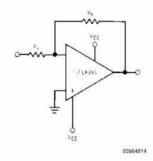

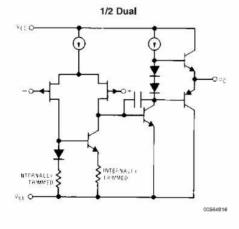

These devices are low cost, high speed, dual JFET input operational amplifiers with an internally trimmed input offset voltage (BI-FET II™ technology). They require low supply current yet maintain a large gain bandwidth product and fast slew rate. In addition, well matched high voltage JFET input devices provide very low input bias and offset currents. The LF353 is pin compatible with the standard LM1558 allowing designers to immediately upgrade the overall performance of existing LM1558 and LM358 designs.

These amplifiers may be used in applications such as high speed integrators, fast D/A converters, sample and hold circuits and many other circuits requiring low input offset voltage, low input bias current, high input impedance, high slew rate and wide bandwidth. The devices also exhibit low noise and offset voltage drift.

### **Features**

| internally trimined onset voltage. | 10 111             |

|------------------------------------|--------------------|

| ■ Low input bias current:          | 50p/               |

| ■ Low input noise voltage:         | 25 nV/√H;          |

| ■ Low input noise current:         | 0.01 pA/√H         |

| ■ Wide gain bandwidth:             | 4 MH               |

| ■ High slew rate:                  | 13 V/µ:            |

| ■ Low supply current:              | 3.6 m/             |

| ■ High input impedance:            | 10 <sup>12</sup> 0 |

| ■ Low total harmonic distortion :  | ≤0.02%             |

| ■ Low 1/f noise corner:            | 50 H               |

■ Low 1/r noise corner: 50 Hz

■ Fast settling time to 0.01%: 2 μs

### **Typical Connection**

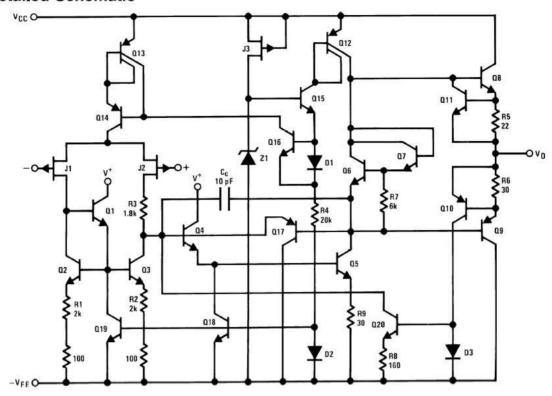

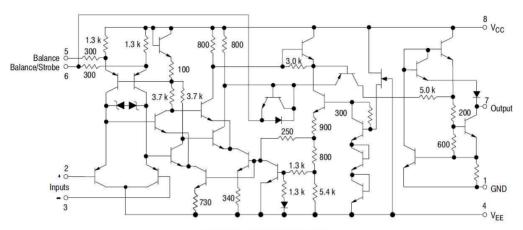

### **Simplified Schematic**

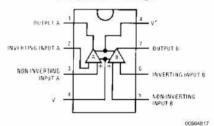

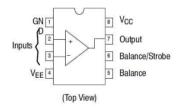

### **Connection Diagram**

Internally trimmed offset voltage

### Dual-In-Line Package

Top View Order Number LF353M, LF353MX or LF353N See NS Package Number M08A or N08E

BI-FET II'm is a trademark of National Semiconductor Corporation.

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage Power Dissipation (Note 2) 0°C to +70°C Operating Temperature Range  $T_i(MAX)$ 150°C Differential Input Voltage ±30V Input Voltage Range (Note 3) ±15V Output Short Circuit Duration Continuous -65°C to +150°C Storage Temperature Range 260°C

Lead Temp. (Soldering, 10 sec.) Soldering Information

Dual-In-Line Package Soldering (10 sec.) Small Outline Package

Vapor Phase (60 sec.) 215°C Infrared (15 sec.) 220°C

See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" for other methods of soldering surface mount devices.

ESD Tolerance (Note 8) 1000V  $\theta_{JA}$  M Package TBD

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

#### **DC Electrical Characteristics**

Note 5)

| Symbol                   | Parameter                          | Conditions                                 | LF353 |                  |     | Units |

|--------------------------|------------------------------------|--------------------------------------------|-------|------------------|-----|-------|

|                          |                                    | 10                                         | Min   | Тур              | Max |       |

| V <sub>OS</sub>          | Input Offset Voltage               | R <sub>S</sub> =10kΩ, T <sub>A</sub> =25°C |       | 5                | 10  | mV    |

|                          | AV 5598                            | Over Temperature                           |       |                  | 13  | mV    |

| $\Delta V_{OS}/\Delta T$ | Average TC of Input Offset Voltage | $R_s=10 \text{ k}\Omega$                   |       | 10               |     | μV/°C |

| os                       | Input Offset Current               | T <sub>j</sub> =25°C, (Notes 5, 6)         |       | 25               | 100 | pA    |

|                          |                                    | T <sub>j</sub> ≤70°C                       |       |                  | 4   | nA    |

| l <sub>B</sub>           | Input Bias Current                 | T <sub>j</sub> =25°C, (Notes 5, 6)         | 81 0  | 50               | 200 | pA    |

|                          |                                    | T <sub>j</sub> ≤70°C                       |       |                  | 8   | nA    |

| R <sub>IN</sub>          | Input Resistance                   | T <sub>j</sub> =25°C                       | 101   | 10 <sup>12</sup> |     | Ω     |

| A <sub>VOL</sub> La      | Large Signal Voltage Gain          | V <sub>S</sub> =±15V, T <sub>A</sub> =25°C | 25    | 100              |     | V/mV  |

|                          |                                    | $V_O=\pm 10V$ , $R_L=2 k\Omega$            |       |                  |     |       |

|                          |                                    | Over Temperature                           | 15    |                  |     | V/mV  |

| Vo                       | Output Voltage Swing               | $V_S=\pm 15V$ , $R_L=10k\Omega$            | ±12   | ±13.5            |     | V     |

| V <sub>CM</sub>          | Input Common-Mode Voltage          | V <sub>S</sub> =±15V                       | ±11   | +15              |     | V     |

|                          | Range                              |                                            |       | -12              |     | V     |

| CMRR                     | Common-Mode Rejection Ratio        | R <sub>S</sub> ≤ 10kΩ                      | 70    | 100              |     | dB    |

| PSRR                     | Supply Voltage Rejection Ratio     | (Note 7)                                   | 70    | 100              |     | dB    |

| Is                       | Supply Current                     | 39 70 %                                    |       | 3.6              | 6.5 | mA    |

260°C

### **AC Electrical Characteristics**

(Note 5)

| Symbol         | Parameter                       | Conditions                                              | LF353 |      |     | Units  |

|----------------|---------------------------------|---------------------------------------------------------|-------|------|-----|--------|

|                |                                 |                                                         | Min   | Тур  | Max |        |

| 2              | Amplifier to Amplifier Coupling | T <sub>A</sub> =25°C, f=1 Hz-20 kHz<br>(Input Referred) |       | -120 |     | dB     |

| SR             | Slew Rate                       | V <sub>S</sub> =±15V, T <sub>A</sub> =25°C              | 8.0   | 13   |     | V/µs   |

| GBW            | Gain Bandwidth Product          | V <sub>S</sub> =±15V, T <sub>A</sub> =25°C              | 2.7   | 4    |     | MHz    |

| e <sub>n</sub> | Equivalent Input Noise Voltage  | $T_A$ =25°C, $R_S$ =100Ω, f=1000 Hz                     |       | 16   |     | nV/√Hz |

| i <sub>n</sub> | Equivalent Input Noise Current  | T <sub>j</sub> =25°C, f=1000 Hz                         |       | 0.01 |     | pA/√Hz |

# **Detailed Schematic**

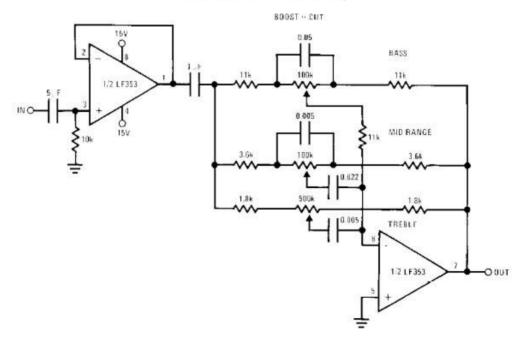

# **Typical Applications**

#### Three-Band Active Tone Control

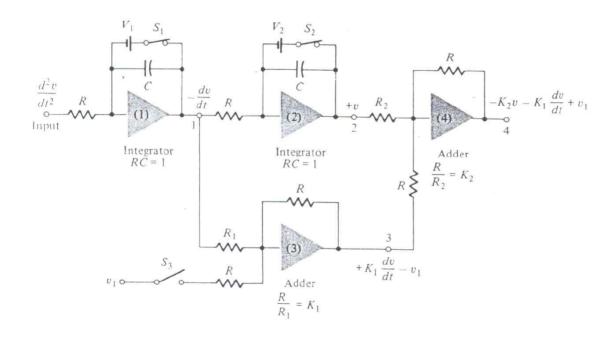

# □ 전자식 아날로그계산기의 예

■ 미분방정식:

$$\frac{d^2v}{dt^2} + K_1 \frac{dv}{dt} + K_2 v - v_1 = 0$$

- $\frac{d^2t}{dt^2}$ 를 전압형태로 얻을 수 있다고 가정

- K<sub>1</sub>, K<sub>2</sub>는 양의 상수

- 전자식 아날로그계산기의 구성도

- t=0에서  $S_1$  및  $S_2$ 를 열고,  $S_3$ 는 닫음

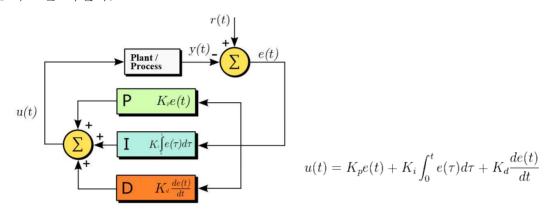

## ■ PID (Proportional-Integral-Derivative) Controller

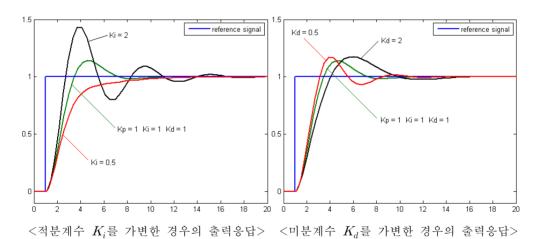

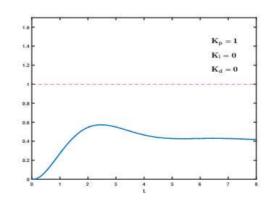

PID 제어기는 기본적으로 피드백(feedback) 제어기의 형태를 가지고 있으며, 실제가장 많이 사용되는 대표적인 형태의 제어기법이다. 제어하고자 하는 대상의 출력값(output)을 측정하고 이를 원하고자 하는 참조값(reference value) 혹은 설정값(setpoint)과 비교하여 오차(error)를 계산한 후, 이 오차값에 대해 비례(Proportional)제어, 적분(Integral)제어 및 미분(Derivative)제어를 조합하여 제어하는 구조를 가진다.

<PID 계수 모두를 가변한 경우의 출력응답>

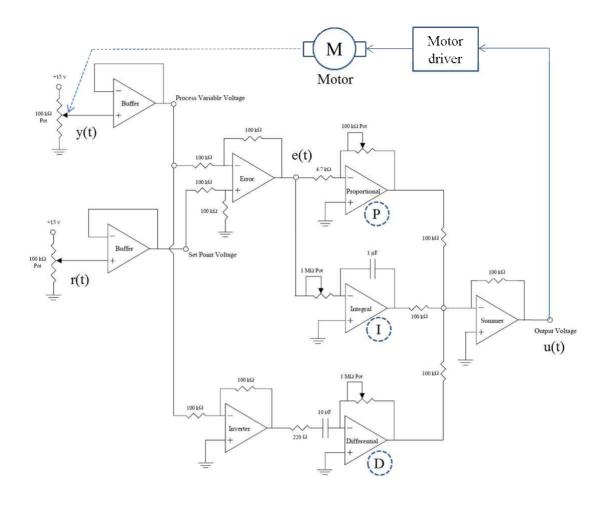

# ■ 아날로그 PID (Proportional-Integral-Derivative) 제어회로 예

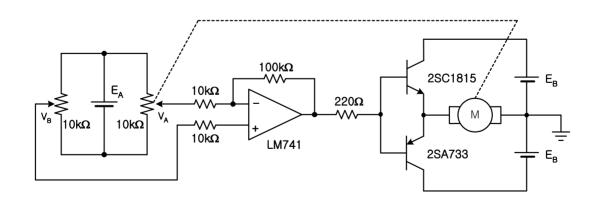

# ■ 비례제어 위치제어 회로 예

# LM211, LM311

# **Single Comparators**

The ability to operate from a single power supply of 5.0 V to 30 V or  $\pm$  15 V split supplies, as commonly used with operational amplifiers, makes the LM211/LM311 a truly versatile comparator. Moreover, the inputs of the device can be isolated from system ground while the output can drive loads referenced either to ground, the  $\rm V_{CC}$  or the  $\rm V_{EE}$  supply. This flexibility makes it possible to drive DTL, RTL, TTL, or MOS logic. The output can also switch voltages to 50 V at currents to 50 mA, therefore, the LM211/LM311 can be used to drive relays, lamps or solenoids.

#### **Features**

• Pb-Free Packages are Available

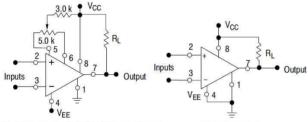

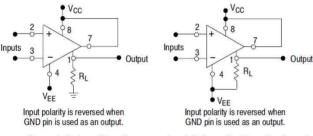

Split Power Supply with Offset Balance

Single Supply

**Ground-Referred Load**

Load Referred to Negative Supply

Figure 1. Typical Comparator Design Configurations

#### ON Semiconductor®

http://onsemi.com

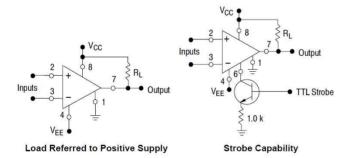

#### PIN CONNECTIONS

# ORDERING & DEVICE MARKING INFORMATION

See detailed ordering and shipping information and marking information in the package dimensions section on page 7 of

### LM211, LM311

Figure 2. Circuit Schematic

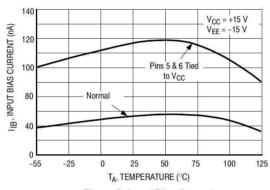

Figure 3. Input Bias Current versus Temperature

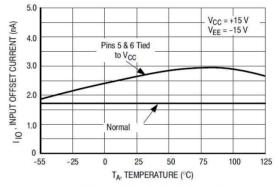

Figure 4. Input Offset Current versus Temperature

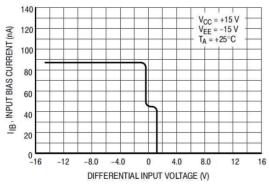

Figure 5. Input Bias Current versus Differential Input Voltage

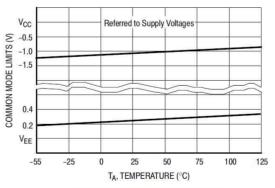

Figure 6. Common Mode Limits versus Temperature

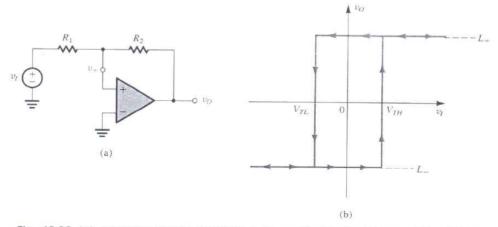

# ■ Schmitt trigger 회로

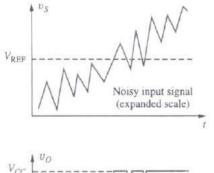

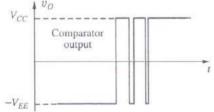

Figure 12.68 Comparator response to noisy input signal.

Figure 12.69 Schmitt-trigger circuit.

FIGURE 19.22 Schmitt trigger input and output signals.

FIGURE 19.23 The UTP and LTP

FIGURE 19.24 Schmitt trigger hysteresis.

Fig. 12.19 (a) The bistable circuit of Fig. 12.17 with the negative input terminal of the op amp disconnected from ground and connected to an input signal  $v_i$ . (b) The transfer characteristic of the circuit in (a) for increasing  $v_i$ . (c) The transfer characteristic for decreasing  $v_i$ . (d) The complete transfer characteristics.

**Fig. 12.20 (a)** A bistable circuit derived from the positive-feedback loop of Fig. 12.17 by applying  $v_i$  through  $R_1$ . **(b)** The transfer characteristic of the circuit in (a) is noninverting. (Compare it to the inverting characteristic in Fig. 12.19d.)